Intel Pentium 4 Processor on 90 nm Process

Table Of Contents

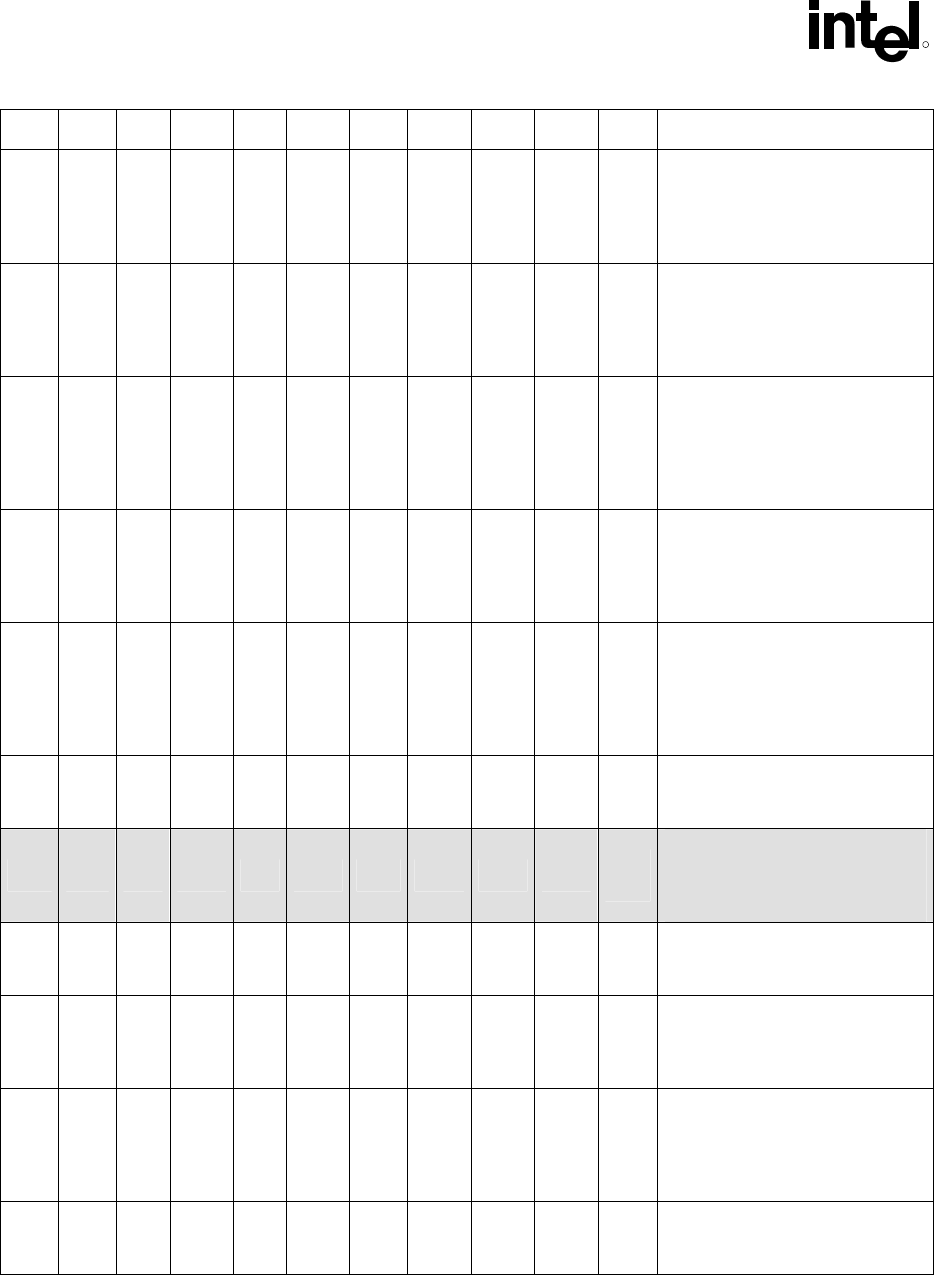

Summary Tables of Changes

R

16 Intel

®

Pentium

®

4 Processor on 90 nm Process Specification Update

NO. C0

1

D0 LD0

2

E0 LE0

2

G1

1

LG1

2

LN0

2

LR0

2

Plan ERRATA

R87 X Fixed

FXSAVE Instruction May Result in

Incorrect Data on Processors

Supporting Intel® Extended

Memory 64 Technology (Intel®

EM64T)

R88 X Fixed

Compatibility Mode STOS

Instructions May Alter RSI Register

Results on a Processor Supporting

Intel® Extended Memory 64

Technology (Intel® EM64T)

R89 X Fixed

LDT Descriptor Which Crosses 16

bit Boundary Access Does Not

Cause a #GP Fault on a Processor

Supporting Intel® Extended

Memory 64 Technology (Intel®

EM64T)

R90 X Fixed

Upper Reserved Bits are Incorrectly

Checked While Loading PDPTR's

on a Processor Supporting Intel®

Extended Memory 64 Technology

(Intel® EM64T)

R91 X X X X X

No

Fix

A 64-Bit Value of Linear Instruction

Pointer (LIP) May be Reported

Incorrectly in the Branch Trace

Store (BTS) Memory Record or in

the Precise Event Based Sampling

(PEBS) Memory Record

R92 X X X X X X X X Fixed

It is Possible That Two specific

Invalid Opcodes May Cause

Unexpected Memory Accesses

R93 X X X X X X X X X

No

Fix

At Core-to-bus Ratios of 16:1 and

Above Defer Reply Transactions

with Non-zero REQb Values May

Cause a Front Side Bus Stall

R94 X X X X X X X X X

No

Fix

The Processor May Issue Front

Side Bus Transactions up to 6

Clocks after RESET# is Asserted

R95 X X X X X X X X X

No

Fix

Front Side Bus Machine Checks

May be Reported as a Result of On-

Going Transactions during Warm

Reset

R96 X Fixed

CPUID Feature Flag Reports

LAHF/SAHF as Unavailable

however the Execution of

LAHF/SAHF May Not Result in an

Invalid Opcode Exception

R97 X5 X5 X5 X5 X5 X5 X5 X5 X

No

Fix

The Processor May Issue Multiple

Code Fetches to the Same Cache

Line for Systems with Slow Memory