Intel Pentium 4 Processor on 90 nm Process

Table Of Contents

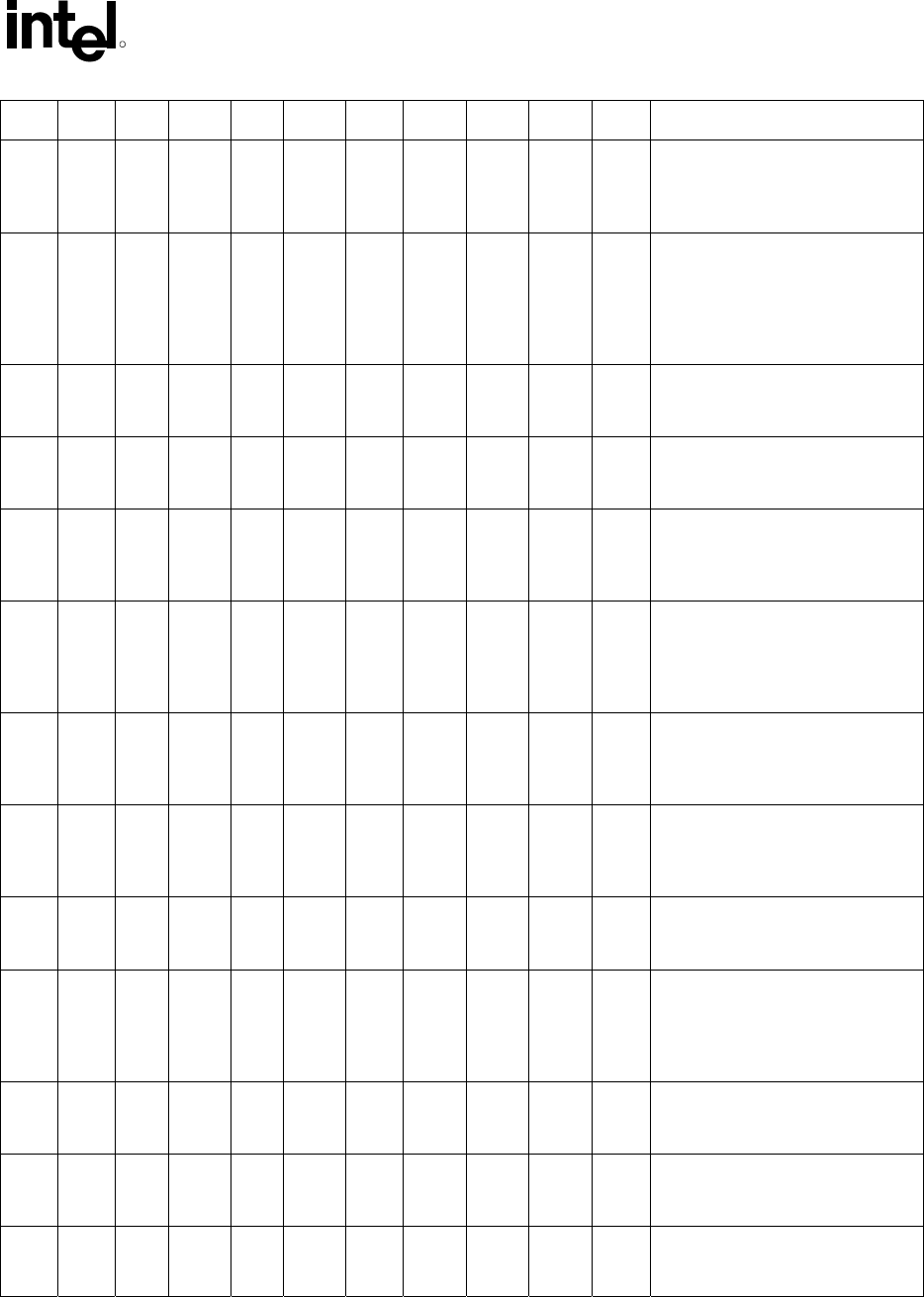

Summary Tables of Changes

R

Intel

®

Pentium

®

4 Processor on 90 nm Process Specification Update 17

NO. C0

1

D0 LD0

2

E0 LE0

2

G1

1

LG1

2

LN0

2

LR0

2

Plan ERRATA

R98 X X X X X X X X X

No

Fix

Writing the Local Vector Table

(LVT) when an Interrupt is Pending

May Cause an Unexpected

Interrupt

R99 X

No

Fix

Access to an Unsupported Address

Range in Uniprocessor (UP) or

Dual-processor (DP) Systems

Supporting Intel® Virtualization

Technology May Not Trigger

Appropriate Actions

R100 X

No

Fix

VM Exit Due to a MOV from CR8

May Cause an Unexpected Memory

Access

R101 X

No

Fix

The Processor May Incorrectly

Respond to Machine Checks during

VM Entry/Exit Transitions

R102 X

No

Fix

INIT during String Operations in the

Virtual-Machine Extension (VMX)

Guest Mode May Cause

Unexpected System Behavior

R103 X

No

Fix

Power Down Requests May not be

Serviced if a Power Down

Transition is Interrupted by an In-

Target Probe Event in the Presence

of a Specific Type of VM Exit

R104 X

No

Fix

VM EXIT Due to TPR shadow

Below Threshold May Improperly

Set and Cause "Blocking by STI"

actions

R105 X

No

Fix

VM Entry/Exit Writes to

LSTAR/SYSCALL_FLAG MSR's

May Cause Incorrect Data to be

Written to Bits [63:32]

R106 X

No

Fix

Machine Check Architecture

Multiple Data Parity Errors May be

Reported

R107 X

Plan

Fix

Attempting to Use an LDT Entry

when the LDTR Has Been Loaded

with an Unusable Segment May

Cause Unexpected Memory

Accesses

R108 X

No

Fix

The Execution of a VMPTRLD

Instruction May Cause an

Unexpected Memory Access

R109 X

No

Fix

The Execution of VMPTRLD or

VMREAD May Cause an

Unexpected Memory Access

R110 X X X X X

No

Fix

IRET under Certain Conditions May

Cause an Unexpected Alignment

Check Exception