Intel Pentium 4 Processor on 90 nm Process

Table Of Contents

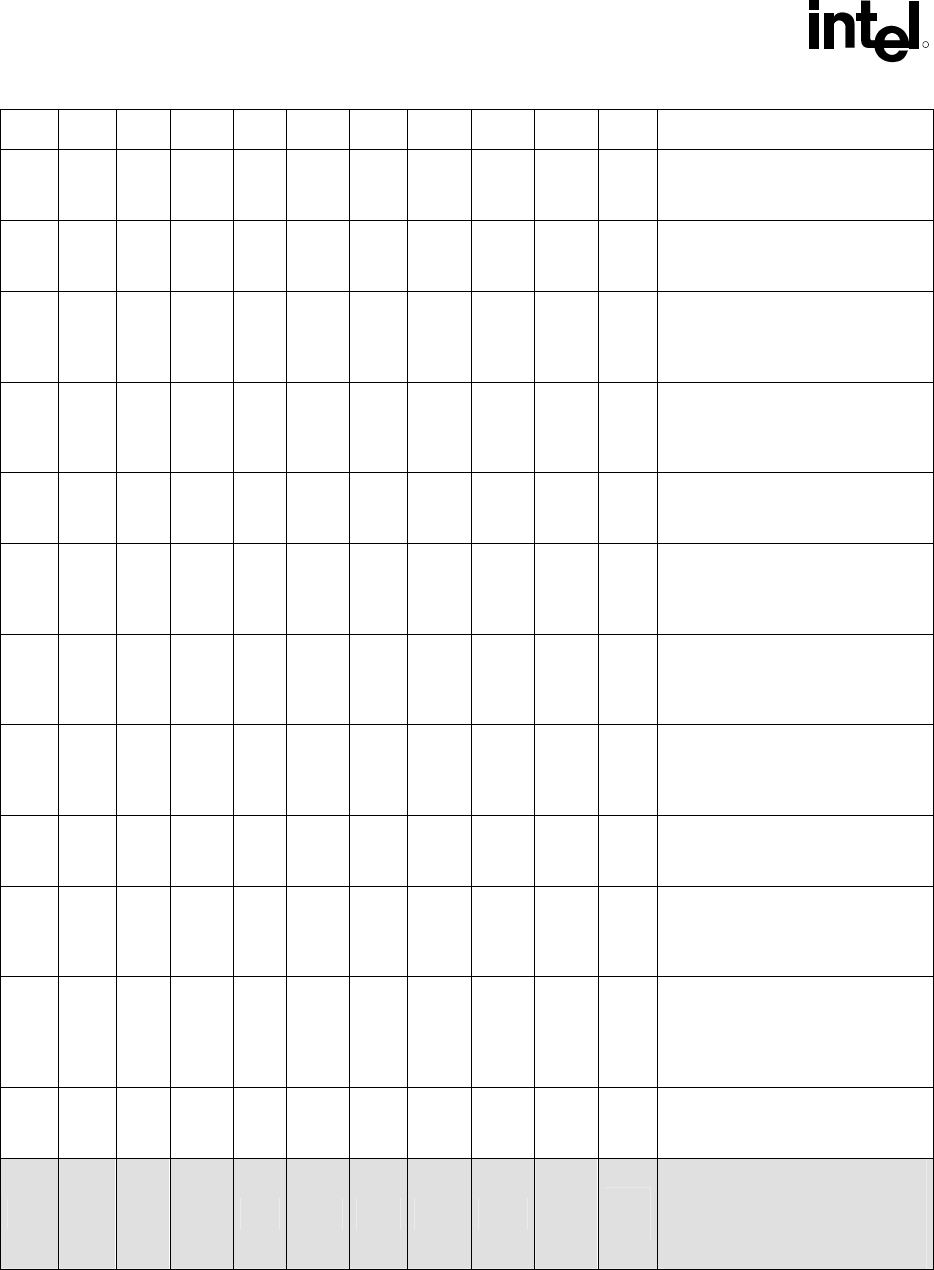

Summary Tables of Changes

R

18 Intel

®

Pentium

®

4 Processor on 90 nm Process Specification Update

NO. C0

1

D0 LD0

2

E0 LE0

2

G1

1

LG1

2

LN0

2

LR0

2

Plan ERRATA

R111 X

No

Fix

FS/GS Base MSRs can be Loaded

from MSR-Load Areas during VM

Entry or VM Exit

R112 X

Plan

Fix

NMI-blocking Information Recorded

in VMCS May be Incorrect after a

#GP on an IRET Instruction

R113 X

Plan

Fix

VMLAUNCH/VMRESUME May Not

Fail when VMCS is Programmed to

Cause VM Exit to Return to a

Different Mode

R114 X Fixed

Upper 32 bits of ‘From’ Address

Reported through LBR or LER

MSRs, BTMs or BTSs May be

Incorrect

R115 X

Plan

Fix

VMEntry from 64-bit Host to 32-bit

Guest may Cause IERR# with

Hyper-Threading Enabled

R116 X X X X X X X X X

No

Fix

L2 Cache ECC Machine Check

Errors May be erroneously Reported

after an Asynchronous RESET#

Assertion

R117 X

Plan

Fix

VMExit after MOV SS and a Waiting

x87 Instruction May not Clear the

Interruptibility State in the VMM’s

Working VMCS

R118 X

Plan

Fix

VMCALL to Activate Dual-monitor

Treatment of SMIs and SMM

Ignores Reserved Bit settings in

VM-exit Control Field

R119 X X X X X X X X X

No

Fix

Using 2M/4M Pages When A20M#

Is Asserted May Result in Incorrect

Address Translations

R120 X X X X X X X X X

No

Fix

Writing Shared Unaligned Data that

Crosses a Cache Line without

Proper Semaphores or Barriers May

Expose a Memory Ordering Issue

R121 X X X X X X X X X

No

Fix

The IA32_MC0_STATUS and

IA32_MC1_STATUS Overflow Bit is

not set when Multiple Un-

correctable Machine Check Errors

Occur at the Same Time

R122 X X X X X X X X X

No

Fix

Debug Status Register (DR6)

Breakpoint Condition Detected

Flags May be set Incorrectly

R123 X X X X X X X X X

No

Fix

A Continuous Loop Executing Bus

Lock Transactions on One Logical

Processor may Prevent Another

Logical Processor from Acquiring

Resources

NOTES:

1. Only applies to Pentium

®

4 processor on 90 nm Process in the 478-pin package

2. Prefix “L” denotes Pentium 4 processor on 90 nm Process in the 775-land LGA package