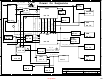

Mobile Intel Pentium 4 Processor - M and Intel 845MP/MZ Chipset Platform Design Guide

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

SIO

Enable

Disable

J49

1-2 (Default)

2-3

Super I/O Controller

31 42

845MP/MZ Platformm

Title

Sheet of

Project:

+V5S_DIODE

BUSY/WAIT#

PD6

AFD#/DSTRB#

PD0

PD4

ACK#

STB#/WRITE#

PD1

PD7

SIO_RST#

PD5

PD2

PD3

+V5S 4,9,17,19,20,24,32,33,35,36,37,40

+V3.3S_SIO

+V3.3S4,5,6,9,10,14,17,19,23,28,29,30,32,33,36,37,40

+V3.3S_SIO

+V3.3S_SIO

PPT_PD5 32

PPT_PD0 32

PPT_PD1 32

PPT_PD2 32

PPT_PD3 32

PPT_PD4 32

PPT_PD6 32

PPT_PD7 32

LPC_AD116,28,29,30,34

LPC_AD216,28,29,30,34

PM_CLKRUN#16,22,29,34

LPC_AD316,28,29,30,34

INT_SERIRQ15,18,19,20,29,34

LPC_AD016,28,29,30,34

LPC_FRAME#16,28,29,30,34

IR_SEL32

IR_MD032

IR_MD132

PPT_PNF# 32

PPT_PE 32

PPT_ERR# 32

PPT_ACK# 32

PPT_BUSY/WAIT# 32

PPT_SLCT 32

FLP_DIR#32

FLP_STEP#32

LPC_DRQ#016,22,34

FLP_DRATE032

FLP_MTR0#32

FLP_DR0#32

FLP_HDSEL#32

FLP_DENSEL#32

FLP_WGATE#32

FLP_WDATA#32

IR_TXD32

SMC_EXTSMI#16,29,33,34

PPT_INIT# 32

PPT_AFD#/DSTRB# 32

PPT_STB#/WRITE# 32

SER_SOUTA 20,32

PPT_SLIN#/ASTRB# 32

FLP_INDEX#32

FLP_WP#32

CLK_SIO1414

FLP_RDATA#32

CLK_SIOPCI14

PM_SUS_STAT#9,16,29,34

PCI_RST_ONBD#

4,15,20,28,29,30,34

FLP_TRK0#32

FLP_DSKCHG#32

IR_RXD32

SER_DCDA# 20,32

SER_RIA# 20,32

SER_DTRA# 20,32

SER_DSRA# 20,32

SER_SINA 20,32

SER_CTSA# 20,32

SER_RTSA# 20,32

RP59C

4.7K

3 6

RP57C 33

3 6

RP57B 33

2 7

R175 100

RP57A 33

1 8

RP74A 10K

1 8

RP55D

1K

45

RP56D 33

4 5

RP55C

1K

36

C514

0.1UF

C287

330PF

R173 100

C508

0.1UF

C502

330PF

RP58A

1K

18

RP56C 33

3 6

C289

330PF

RP55B

1K

27

RP56A 33

1 8

C507

330PF

C285

330PF

RP56B 33

2 7

RP41D

4.7K

4 5

C305

680PF

C303

680PF

CON3_HDR

J49

3

2

1

Bus Interface

Clock

IR

FDC

Parallel PortSerial Port PWR & GND

GPIOs

Straps

U30

PC87393

98

1

42

3

15

96

99

100

2

43

16

44

97

17

18

46

81

8

80

48

11

50

12

52

9

10

19

7

6

20

69

68

67

71

66

70

33

29

49

30

41

72

34

73

21 45

51

22

31

84

23

28

47

25

27

37

26

36

24

82

83

53

40

54

35

60

55

56

61

62

58

59

4

5

32

14

39

63

88

13

38

64

89

79

78

77

76

75

74

57

85

86

87

90

91

92

93

94

95

65

GPIO5

GPIO2

PD7

GPIO0

LAD0

GPIO7

GPIO4

GPIO3

GPIO1

PD6

LAD1

PD5

GPIO6

LAD2

LAD3

PD3

GPIO10

LCLK

GPIO11

PD2

LDRQ#

PD1

LFRAME#

PD0

LRESET#

SERIRQ

SMI#

LPCPD#

CLKRUN#

CLKIN

IRRX1

IRRX2_IRSL0

IRSL1

IRSL2A/DR1B/XIORDB

IRSL3/PWUREQ

IRTX

DENSEL

DIR#

INIT#

DR0#

ACK#

DR1#

DRATE0

MTR1#

DSKCHG# PD4

ERR#

HDSEL#

MTR0#

GPIO31

RDATA#

STEP#

SLIN#/ASTRB#

TRK0#

WDATA#

PE

WGATE#

SLCT

WP#

GPIO33

GPIO32

AFD#/DSTRB#

BUSY/WAIT#

STB#/WRITE#

PNF

CTS1#

DCD1#

DSR1#

DTR1#

RI1#

RTS1#

SOUT1/XCNF0

XCNF1/XWR#

GPIO34

INDEX#

VDD1

VDD2

VDD3

VDD4

VSS5

VSS6

VSS7

VSS8

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

SIN1

GPIO30

GPIO27

GPIO26

XCNF2

GPIO24

GPIO23

GPIO22

GPIO21

GPIO20

NC

RP59B

4.7K

2 7

R161 33

R165

4.7K

RP58D

1K

45

R159

10K

R424

33

RP58C

1K

36

RP74C

10K

3 6

R182

NO_STUFF_0.01_1%

12

RP59D

4.7K

4 5

RP41A

4.7K

1 8

Q19

BAR43

RP55A

1K

18

RP58B

1K

27

C500

330PF

C501

330PF

C301

330PF

RP41C

4.7K

3 6

C302

330PF

C286

330PF

RP41B

4.7K

2 7

RP59A

4.7K

1 8

C282

22UF

R160 33

241

Design Guide