Mobile Intel Pentium 4 Processor - M and Intel 845MP/MZ Chipset Platform Design Guide

Mobile Intel

®

Pentium

®

4 Processor-M and Intel

®

845MP/845MZ Chipset Platform

Design Guide 31

R

Table 6. Processor System Bus Address Signal Routing Guidelines

Signal Names

Routing Length

(pin-to-pin) L1

CPU

Intel

845MP/845MZ

Topology

Max

(inches)

Min

(inches)

Nominal

Impedance

(ohms)

Width &

Spacing

(mils)

A[35:3]# HA[35:3]# Stripline 10.0 1.5 55 ± 15% 4 & 8

REQ[4:0]# HREQ[4:0]# Stripline 10.0 1.5 55 ± 15% 4 & 8

ADSTB[1:0]# HADSTB[1:0]# Stripline 10.0 1.5 55 ± 15% 4 & 8

NOTE: The Address signals within each group must be routed to within ± 0.200 of its associated strobe. . All traces

within each signal group must be routed on the same layer (required). Intel recommends that the length of

the strobes be centered to the average length of associated data or address traces to maximize setup/hold

time margins.

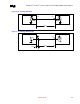

Figure 5. SS Topology for Address and Data

Processor

Chipset

Vtt

Pin

Pad

Pin

Pad

Vtt

L1