Mobile Intel Pentium 4 Processor - M and Intel 845MP/MZ Chipset Platform Design Guide

Mobile Intel

®

Pentium

®

4 Processor-M and Intel

®

845MP/845MZ Chipset Platform

38 Design Guide

R

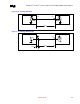

3.4.4.2. Voltage Translator Circuit

This recommended Voltage translator circuit should be applied to topologies #1 and #2B shown in

Section 3.4.4.1.1 and 3.4.4.1.3.

Figure 12. Voltage Translator Circuit of Topology#1 and #2B

Vcc of Receiver

To Receiver

From Driver

470 ohm

+/- 5%

470 ohm

+/- 5%

3904

3904

3.5. ITP Debug Port

Note: The Debug Port design information has been moved! This includes all information necessary to develop

a Debug Port on this platform, including electrical specifications, mechanical requirements, and all In-

Target Probe (ITP) signal layout guidelines. Please reference the

Intel

®

Pentium

®

4 Debug Port Design

Guide

and the ITP700 Debug Port Design Guide, which can be found on

http://developer.intel.com/design/Xeon/guides/249679.htm, for the design of your platform. Refer to the

ITP700 Debug Port Design Guide for further information Debug Tools Specifications.

3.5.1.1. Logic Analyzer Interface (LAI)

Intel is working with two logic analyzer vendors to provide logic analyzer interfaces (LAIs) for use in

debugging the Mobile Intel Pentium 4 Processor-M system. Tektronix* and Agilent* should be contacted

to get specific information about their logic analyzer interfaces. The following information is general in

nature. Specific information must be obtained from the logic analyzer vendor.

Due to the complexity of the Mobile Pentium 4 Processor-M system, the LAI is critical in providing the

ability to probe and capture system bus signals. There are two sets of considerations to keep in mind

when designing a Mobile Pentium 4 Processor-M that use LAI: mechanical and electrical.

3.5.1.1.1. Mechanical Considerations

The LAI is installed between the processor socket and the Mobile Pentium 4 processor. The LAI pins

plug into the socket, while the Mobile Pentium 4 Processor-M in the 478-pin package plugs into a socket

on the LAI. Cabling that is part of the LAI egresses the system to allow an electrical connection between

the Mobile Pentium 4 Processor-M and a logic analyzer. The maximum volume occupied by the LAI,

known as the keep-out volume, as well as the cable egress restrictions, should be obtained from the logic

analyzer vendor. System designers must make sure that the keep-out volume remains unobstructed inside

the system. Note that it is possible that the keep-out volume reserved for the LAI may include space