Mobile Intel Pentium 4 Processor - M and Intel 845MP/MZ Chipset Platform Design Guide

Mobile Intel

®

Pentium

®

4 Processor-M and Intel

®

845MP/845MZ Chipset Platform

88 Design Guide

R

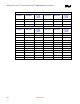

Table 26. Layout Routing Guidelines for AGP 1X Signals

1X signals Max. length (inches) Width (mils) Space (mils)

CLK_AGP_SLT 10 4 4

AGP_PIPE# 10 4 4

AGP_RBF# 10 4 4

AGP_WBF# 10 4 4

AGP_ST[2:0] 10 4 4

AGP_FRAME# 10 4 4

AGP_IRDY# 10 4 4

AGP_TRDY# 10 4 4

AGP_STOP# 10 4 4

AGP_DEVSEL# 10 4 4

AGP_REQ# 10 4 4

AGP_GNT# 10 4 4

AGP_PAR 10 4 4

6.3.1.2. Trace Spacing Requirements

AGP 1X timing domain signals (refer to Table 27) can be routed with 4-mil minimum trace separation.

6.3.1.3. Trace Length Mismatch

There are no trace length mismatch requirements for 1X timing domain signals. These signals must meet

minimum and maximum trace length requirements.

6.3.2. 2X/4X Timing Domain Routing Guidelines

6.3.2.1. Trace Length Requirements for AGP 2X/4X

These trace length guidelines apply to ALL of the signals listed as 2X/4X timing domain signals in Table

25. In addition to these maximum trace length requirements, these signals must meet the trace spacing

and trace length mismatch requirements in Sections 6.3.2.2 and 6.3.2.3.

The maximum line length and mismatch requirements are dependent on the routing rules used on the

motherboard. These routing rules were created to give design freedom by making tradeoffs between

signal coupling (trace spacing) and line lengths. These routing rules are divided by trace spacing. In 1:2

spacing, the distance between the traces is two times the width of traces. Simulations in mobile

environment support this rule.