Technical Product Specification

Appendix E: POST Code Diagnostic LED Decoder Intel® Server Boards S5520HC, S5500HCV, and S5520HCT TPS

Revision 1.9

Intel order number E39529-013

162

Upper nibble bits = 1110b = Eh; Lower nibble bits = 1101b = Dh; the two are

concatenated as EDh. Find the meaning of POST Code EDh in below table – Memory

Population Error: RDIMMs and UDIMMs cannot be mixed in the system.

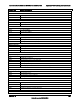

Table 85. POST Codes and Messages

Progress Code

Progress Code Definition

Multi-use Code

This POST Code is used in different contexts

0xF2

Seen at the start of Memory Reference Code (MRC)

Start of the very early platform initialization code

Very late in POST, it is the signal that the OS has switched to virtual memory mode

Memory Error Codes (Accompanied by a beep code)

These codes are used in early POST by Memory Reference Code. Later in POST these same codes are used for

other Progress Codes. These progress codes are subject to change as per Memory Reference Code

0xE8

No Usable Memory Error: No memory in the system, or SPD bad so no memory could be

detected, or all memory failed Hardware BIST. System is halted.

0xEB

Memory Test Error: One or memory DIMMs/Channels failed Hardware BIST, but usable memory

remains. System continues POST.

0xED

Population Error: RDIMMs and UDIMMs cannot be mixed in the system.

0xEE

Mismatch Error: more than 2 Quad Ranked DIMMS in a channel.

Host Processor

0x04

Early processor initialization where system BSP is selected

0x10

Power-on initialization of the host processor (Boot Strap Processor)

0x11

Host processor cache initialization (including AP)

0x12

Starting application processor initialization

0x13

SMM initialization

Chipset

0x21

Initializing a chipset component

Memory

0x22

Reading configuration data from memory (SPD on DIMM)

0x23

Detecting presence of memory

0x24

Programming timing parameters in the memory controller

0x25

Configuring memory parameters in the memory controller

0x26

Optimizing memory controller settings

0x27

Initializing memory, such as ECC init

0x28

Testing memory

PCI Bus

0x50

Enumerating PCI buses

0x51

Allocating resources to PCI buses

0x52

Hot-plug PCI controller initialization

0x53-0x57

Reserved for PCI Bus