Datasheet

LT6555

12

6555f

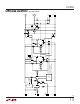

Figure 5. Demo Board Schematic

5

IN1A

4

3

2

5

IN2A

4

3

2

5

IN3A

4

3

2

5

IN1B

4

3

2

5

IN2B

4

3

2

5

IN3B

4

3

2

IN1B

AGND1

IN3A

V

REF

V

REF

IN2A

DGND

DGND

IN1A

AGND2

8

9

10

11

12

7

6

5

4

3

2

1

17

16

15

14

13

18

19

20

21

22

23

24

V

+

OUT2

V

–

OUT1

IN3B

AGND3

IN2B

V

–

V

+

V

+

V

–

OUT3

V

+

SEL

SEL

EN

V

+

U1 LT6555CGN

EXT GND

13

2

JP5

V

REF

JP12

BNC × 6

DGND

1

1

1

1

1

1

L1

L1

L1

L1

L1

L1

Z = 75

Z = 75

Z = 75

Z = 75

Z = 75

Z = 75

JP13

JP14

JP5

JP6

JP7

J3

BANANA JACK

FLOAT AGND

13

2

JP2

DGND

EXT ENABLE

13

2

JP1

CONTROL

13

V

CC

SEL A/B

AB

DGND

2

JP4

SEL

R7

20k

J1

50Ω BNC

EN

5432

1

R10

75Ω

R11

75Ω

R12

75Ω

R4

75Ω

R5

75Ω

R6

75Ω

2

DUAL

NOTE:

470pF BYPASS CAPACITORS LOCATED

AS CLOSE TO PINS AS POSSIBLE

SINGLE

AGND

JP3

SUPPLY

31

E1

EN

E4

SEL A/B

E2

DGND

E5

V

REF

E3

AGND

R8

50Ω

OPT

Z = 50 Z = 50

EN

5

OUT1

J9

1L2

L2

L2

Z = 75

R1

75Ω

R2

75Ω

R3

75Ω

Z = 75

Z = 75

1

1

J10

J11

J4

BANANA JACK

V

EE

6555 F05

4

3

2

5

OUT2

4

3

2

5

OUT3

V

EE

–3.3V TO –5V

4

3

2

C1

4700pF

C10

4700pF

C11

0.33µF

16V

C2

470pF

C3

470pF

C4

10µF

16V

1206

C7

470pF

J2

BANANA JACK

V

CC

V

CC

3.3V TO 5V

C8

0.33µF

C5

4700pF

C6

470pF

C9

10µF

16V

1206

BNC × 3

5432

1

R9

50Ω

OPT

J8

50Ω BNC

Figure 6. Demo Board Topside

(IC Removed for Clarity)

Figure 7. Demo Board Bottom Side

TYPICAL APPLICATIO

U