Datasheet

LTC2351-14

9

235114fb

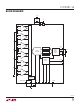

BLOCK DIAGRAM

2

OGND

1

SD0

3

OV

DD

3V

–

+

4

5

24

23

S & H

–

+

7

6

9

12 13

16

19

8

S & H

EXPOSED PAD GND V

REF

10μF

CH0

–

CH0

+

CH1

–

CH1

+

–

+

10

11

S & H

–

+

14

15

S & H

CH2

–

CH2

+

CH3

–

CH3

+

–

+

17

18

S & H

–

+

20

21

S & H

CH4

–

CH4

+

CH5

–

CH5

+

10μF

0.1μF

DGND

32

SCK

30

CONV

SEL2

SEL1 SEL0

THREE-

STATE

SERIAL

OUTPUT

PORT

MUX

2.5V

REFERENCE

TIMING

LOGIC

V

CC

25

3V

V

DD

235114 BD

1.5Msps

14-BIT ADC

14-BIT LATCH 5

14-BIT LATCH 4

14-BIT LATCH 3

14-BIT LATCH 2

14-BIT LATCH 1

14-BIT LATCH 0

26 27

BIP

29 28 31

2233

0.1μF