Datasheet

LTC4308

3

4308f

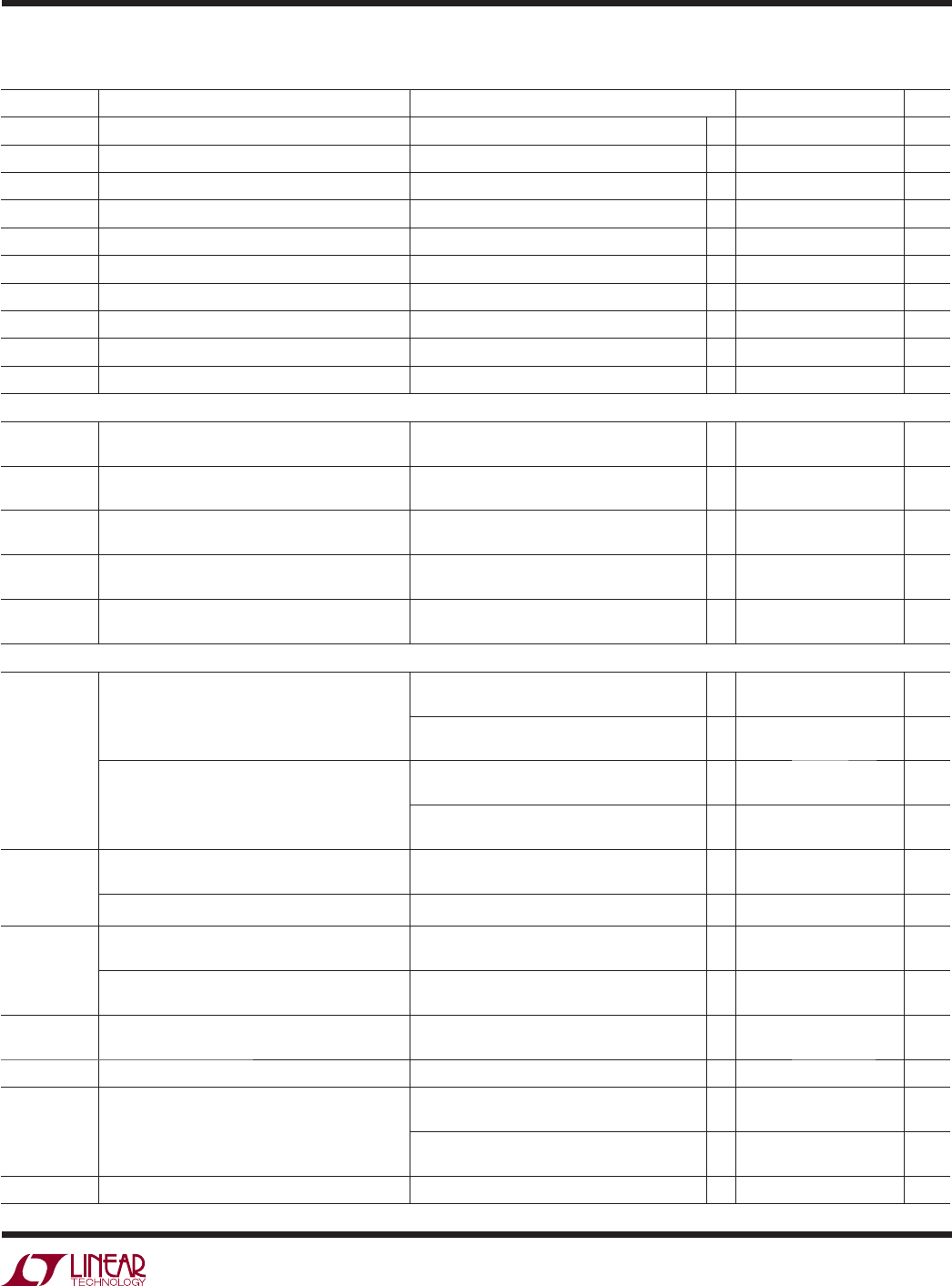

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

t

IDLE

Bus Idle Time

l

55 95 175 μs

V

THR_EN

ENABLE Threshold Voltage ENABLE Rising Edge

l

0.45 0.6 0.75 V

V

THR_EN(HYST)

ENABLE Threshold Voltage Hysteresis (Note 3) 35 mV

I

ENABLE

ENABLE Input Current ENABLE from 0V to V

CC

l

0.1 ±5 μA

t

PLH_EN

ENABLE Delay Off-On (Figure 1) 95 μs

t

PHL_EN

ENABLE Delay On-Off (Note 3), (Figure 1) 10 ns

t

PLH_READY

READY Delay Off-On (Note 3), (Figure 1) 10 ns

t

PHL_READY

READY Delay On-Off (Note 3), (Figure 1) 10 ns

V

OL_READY

READY Output Low Voltage I

READY

= 3mA, V

CC

= 2.3V

l

0.4 V

I

OFF_READY

READY Off Leakage Current V

CC

= READY = 5.5V

l

0.1 ±5 μA

Prop Delay and Rise-Time Accelerators

t

PHL

SDA/SCL Propagation Delay High to Low C

LOAD

= 50pF, 2.7k to V

CC

on SDA, SCL,

(Notes 2, 3), (Figure 1)

70 ns

t

PLH

SDA/SCL Propagation Delay Low to High C

LOAD

= 50pF, 2.7k to V

CC

on SDA, SCL,

(Notes 2, 3), (Figure 1)

10 ns

t

RISE

SDA/SCL Transition Time Low to High C

LOAD

= 100pF, 10k to V

CC

on SDA, SCL,

(Notes 3, 4), (Figure 1)

30 300 ns

t

FALL

SDA/SCL Transition Time High to Low C

LOAD

= 100pF, 10k to V

CC

on SDA, SCL,

(Notes 3, 4), (Figure 1)

30 300 ns

I

PULLUPAC

Transient Boosted Pull-Up Current Positive Transition > 0.8V/μs on SDAOUT,

SCLOUT (Note 5)

58 mA

Input-Output Connection

V

OS

Input to Output Offset Voltage (OUT – IN) 2.7k to V

CC

on SDAOUT, SCLOUT,

SDAIN = SCLIN = 0.2V

l

250 300 380 mV

2.7k to V

CC

on SDAOUT, SCLOUT,

SDAIN = SCLIN = 0.4V, V

CC

= 5.5V

l

250 350 450 mV

Output to Input Offset Voltage (IN – OUT) 2.7k to V

CC

on SDAIN, SCLIN,

SDAOUT = SCLOUT = 0.4V

l

–150 –200 –300 mV

2.7k to V

CC

on SDAIN, SCLIN,

SDAOUT = SCLOUT = 0.4V, V

CC

= 5.5V

l

–150 –250 –350 mV

V

THR

SDAOUT, SCLOUT Logic Input Threshold Voltage V

CC

≥ 2.9V

V

CC

< 2.9V

1.4

1.1

1.65

1.35

1.9

1.6

V

V

SDAIN, SCLIN Logic Input Threshold Voltage SDAIN, SCLIN Rising Edge, V

CC

= 2.3V, 5.5V 0.45 0.6 0.75 V

V

THR(HYST)

SDAOUT, SCLOUT Logic Input Threshold Voltage

Hysteresis

(Note 3) 50 mV

SDAIN, SCLIN Logic Input Threshold Voltage

Hysteresis

(Note 3) 35 mV

C

IN

Digital Input Capacitance SDAIN, SDAOUT,

SCLIN, SCLOUT

(Note 3) 10 pF

I

LEAK

Input Leakage Current SDA, SCL Pins

l

±5 μA

V

OL

Output Low Voltage SDAOUT, SCLOUT Pins, I

SINK

= 4mA,

SDAIN = SCLIN = 0V, V

CC

= 2.7V

l

0 400 mV

2.7k to V

CC

on SDAOUT, SCLOUT,

SDAIN = SCLIN = 0V

l

250 300 380 mV

V

ILMAX

Buffer Input Logic Low Voltage SDAOUT, SCLOUT Pins

l

1.2 V

The l denotes the specifi cations which apply over the full operating

temperature range, otherwise specifi cations are at T

A

= 25°C. V

CC

= 3.3V, unless otherwise noted.

ELECTRICAL CHARACTERISTICS