Instruction Manual

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

125 of 344

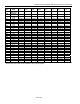

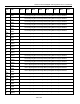

Table 11-8. T1/E1/J1 Transceiver Register Bit Map (Active when CST = 0)

A

DD

R

N

AME

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

000

h

TR.MSTRREG

— — — — TEST1 TEST0 T1/E1 SFTRST

001

h

TR.IOCR1

RSMS RSMS2 RSMS1 RSIO TSDW TSM TSIO ODF

002

h

TR.IOCR2

RDCLKIN

V

TDCLKIN

V

RSYNCINV TSYNCINV TSSYNCINV H100EN TSCLKM RSCLKM

003

h

TR.T1RCR1

— ARC OOF1 OOF2 SYNCC SYNCT SYNCE RESYNC

004

h

TR.T1RCR2

— RFM RB8ZS RSLC96 RZSE — RJC RD4YM

005

h

TR.T1TCR1

TJC TFPT TCPT TSSE GB7S TFDLS TBL TYEL

006

h

TR.T1TCR2

TB8ZS TSLC96 TZSE FBCT2 FBCT1 TD4YM Reserved TB7ZS

007

h

TR.T1CCR1

— — — TRAI-CI TAIS-CI TFM PDE TLOOP

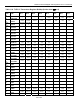

008

h

TR.SSIE1-T1

TR.SSIE1-E1

CH8

CH7

CH7

CH6

CH6

CH5

CH5

CH4

CH4

CH3

CH3

CH2

CH2

CH1

CH1

UCAW

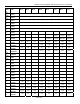

009

h

TR.SSIE2-T1

TR.SSIE2-E1

CH16

CH15

CH15

CH14

CH14

CH13

CH13

CH12

CH12

CH11

CH11

CH10

CH10

CH9

CH9

CH8

00A

h

TR.SSIE3-T1

TR.SSIE3-E1

CH24

CH22

CH23

CH21

CH22

CH20

CH21

CH19

CH20

CH18

CH19

CH17

CH18

CH16

CH17

LCAW

00B

h

TR.SSIE4

CH30 CH29 CH28 CH27 CH26 CH25 CH24 CH23

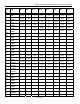

00C

h

TR.T1RDMR1

CH8 CH7 CH6 CH5 CH4 CH3 CH2 CH1

00D

h

TR.T1RDMR2

CH16 CH15 CH14 CH13 CH12 CH11 CH10 CH9

00E

h

TR.T1RDMR3

CH24 CH23 CH22 CH21 CH20 CH19 CH18 CH17

00F

h

TR.IDR

ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

010

h

TR.INFO1

RPDV TPDV COFA 8ZD 16ZD SEFE B8ZS FBE

011

h

TR.INFO2

BSYNC BD TCLE TOCD RL3 RL2 RL1 RL0

012

h

TR.INFO3

— — — — — CRCRC FASRC CASRC

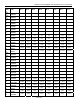

013

h

Reserved

— — — — — — — —

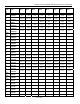

014

h

TR.IIR1

SR8 SR7 SR6 SR5 SR4 SR3 SR2 SR1

015

h

TR.IIR2

— — — — — — — SR9

016

h

TR.SR1

ILUT TIMER RSCOS JALT LRCL TCLE TOCD LOLITC

017

h

TR.IMR1

ILUT TIMER RSCOS JALT LRCL TCLE TOCD LOLITC

018

h

TR.SR2

RYELC RUA1C FRCLC RLOSC RYEL RUA1 FRCL RLOS

019

TR.IMR2

RYELC RUA1C FRCLC RLOSC RYEL RUA1 FRCL RLOS