Instruction Manual

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

129 of 344

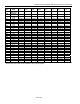

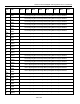

A

DD

R

N

AME

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

06A

h

TR.RS11

Receive Signaling Bit Format Changes With Operating Mode. See Register Definition.

06B

h

TR.RS12

Receive Signaling Bit Format Changes With Operating Mode. See Register Definition.

06C

h

TR.RS13

Receive Signaling Bit Format Changes With Operating Mode. See Register Definition.

06D

h

TR.RS14

Receive Signaling Bit Format Changes With Operating Mode. See Register Definition.

06E

h

TR.RS15

Receive Signaling Bit Format Changes With Operating Mode. See Register Definition.

06F

h

TR.RS16

Receive Signaling Bit Format Changes With Operating Mode. See Register Definition.

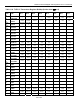

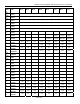

070

h

TR.CCR1

— CRC4R SIE ODM — TCSS1 TCSS0 RLOSF

071

h

TR.CCR2

— — — — — BPCS1 BPCS0 BPEN

072

h

TR.CCR3

— — — — TDATFMT TGPCKEN RDATFMT RGPCKEN

073

h

TR.CCR4

RLT3 RLT2 RLT1 RLT0 UOP3 UOP2 UOP1 UOP0

074

h

TR.TDS0SEL

— — — TCM4 TCM3 TCM2 TCM1 TCM0

075

h

TR.TDS0M

B1 B2 B3 B4 B5 B6 B7 B8

076

h

TR.RDS0SEL

— — — RCM4 RCM3 RCM2 RCM1 RCM0

077

h

TR.RDS0M

B1 B2 B3 B4 B5 B6 B7 B8

078

h

TR.LIC1

L2 L1 L0 EGL JAS JABDS DJA TPD

079

h

TR.LIC2

ETS LIRST IBPV TUA1 JAMUX — SCLD CLDS

07A

h

TR.LIC3

— TCES RCES MM1 MM0 RSCLKE TSCLKE TAOZ

07B

h

TR.LIC4

CMIE CMII MPS1 MPS0 TT1 TT0 RT1 RT0

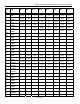

07C

h

Reserved

— — — — — — — —

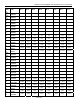

07D

h

TR.TLBC

— AGCD GC5 GC4 GC3 GC2 GC1 GC0

07E

h

TR.IAAR

GRIC GTIC IAA5 IAA4 IAA3 IAA2 IAA1 IAA0

07F

h

TR.PCICR

C7 C6 C5 C4 C3 C2 C1 C0

080

h

TR.TCICE1

CH8 CH7 CH6 CH5 CH4 CH3 CH2 CH1

081

h

TR.TCICE2

CH16 CH15 CH14 CH13 CH12 CH11 CH10 CH9

082

h

TR.TCICE3

CH24 CH23 CH22 CH21 CH20 CH19 CH18 CH17

083

h

TR.TCICE4

CH32 CH31 CH30 CH29 CH28 CH27 CH26 CH25

084

h

TR.RCICE1

CH8 CH7 CH6 CH5 CH4 CH3 CH2 CH1