Owner manual

MAX4888A/MAX4889A

5.0Gbps PCI Express Passive Switches

8 _______________________________________________________________________________________

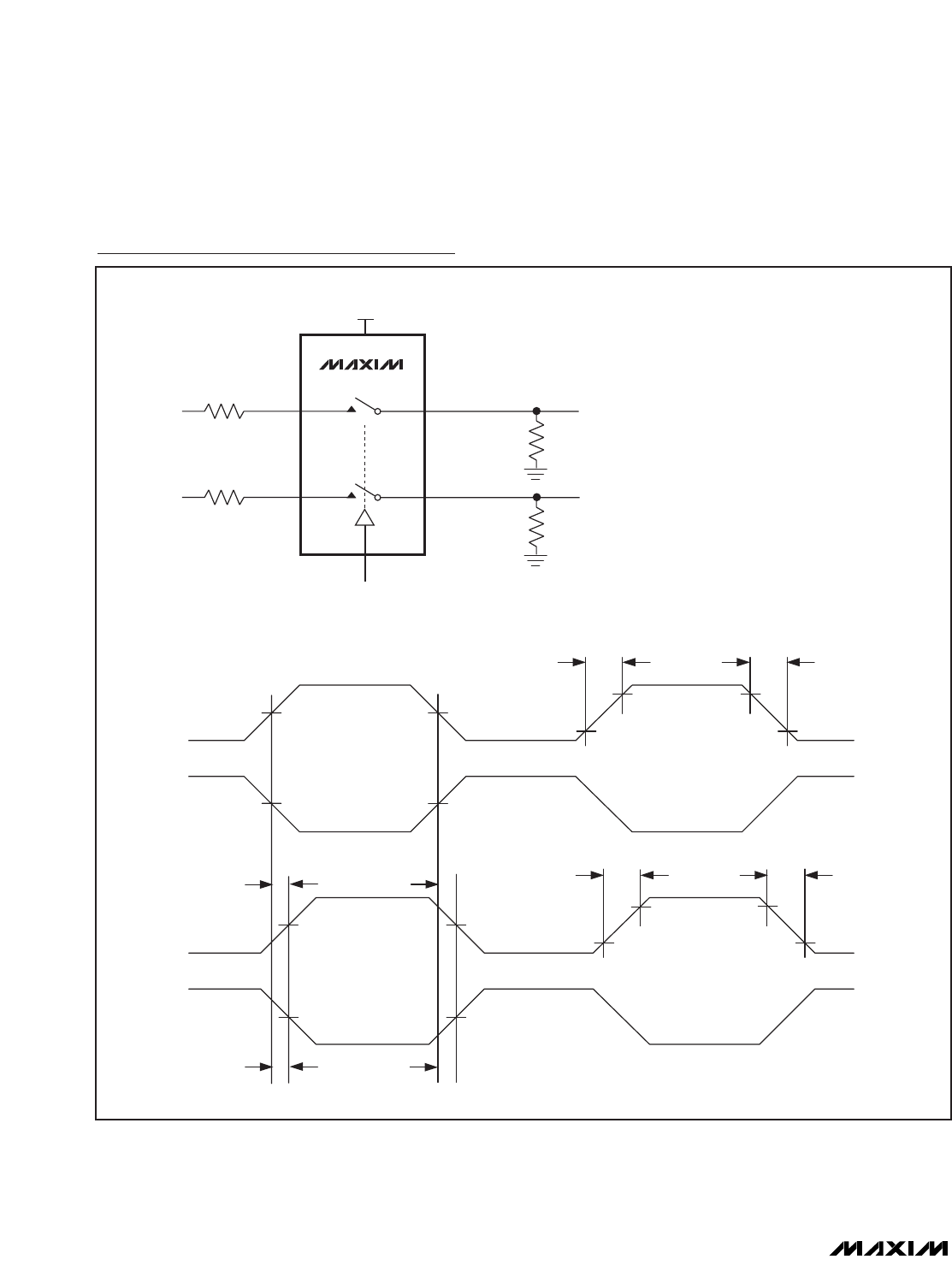

Test Circuits/Timing Diagrams (continued)

IN+

V+

+3.3V

IN-

OUT+

OUT-

V

IN+

V

IN-

V

OUT+

V

OUT-

NO_+ OR

NC_+

NO_- OR

NC_-

SEL

COM

_+

COM

_-

0V

+1.5V

0V

+1.5V

0V

+1.5V

0V

+1.5V

t

PLHX

t

PHLX

t

INRISE

t

OUTRISE

t

OUTFALL

RISE-TIME PROPAGATION DELAY = t

PLHX

OR t

PLHY

FALL-TIME PROPAGATION DELAY = t

PHLX

OR t

PHLY

t

SK1

=

DIFFERENCE IN PROPAGATION DELAY (RISE-FALL)

50%

50%

50%

50%

90%

10% 10%

90%

10% 10%

R

L

R

L

50%

50%

50%

50%

t

INFALL

90%

90%

t

PHLY

t

PLHY

R

S

R

S

MAX4888A/MAX4889A

BETWEEN TWO LINES ON THE SAME PAIR

BETWEEN ANY TWO PAIRS

t

SK2

= | t

PLHX

- t

PHLY

| OR | t

PHLX

- t

PLHY

|

Figure 2. Propagation Delay and Output Skew