Datasheet

55

AT32UC3A

SDRAMC

11

Address Change before SDCK Rising Edge

6.2

ns

SDRAMC

12

Address Change after SDCK Rising Edge

2.2

SDRAMC

13

Bank Change before SDCK Rising Edge

6.3

SDRAMC

14

Bank Change after SDCK Rising Edge

2.4

SDRAMC

15

CAS Low before SDCK Rising Edge

7.4

SDRAMC

16

CAS High after SDCK Rising Edge

1.9

SDRAMC

17

DQM Change before SDCK Rising Edge

6.4

SDRAMC

18

DQM Change after SDCK Rising Edge

2.2

SDRAMC

19

D0-D15 in Setup before SDCK Rising Edge

9

SDRAMC

20

D0-D15 in Hold after SDCK Rising Edge

0

SDRAMC

23

SDWE Low before SDCK Rising Edge

7.6

SDRAMC

24

SDWE High after SDCK Rising Edge

1.8

SDRAMC

25

D0-D15 Out Valid before SDCK Rising Edge

7.1

SDRAMC

26

D0-D15 Out Valid after SDCK Rising Edge

1.5

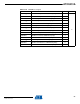

Table 12-28. SDRAM Clock Signal.

Symbol Parameter Min Units

32058KS–AVR32–01/12