Datasheet

19

32072SH–AVR32–10/2012

AT32UC3A3

3.4 I/O Line Considerations

3.4.1 JTAG Pins

TMS and TDI pins have pull-up resistors. TDO pin is an output, driven at up to VDDIO, and has

no pull-up resistor.

3.4.2 RESET_N Pin

The RESET_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIO. As

the product integrates a power-on reset cell, the RESET_N pin can be left unconnected in case

no reset from the system needs to be applied to the product.

3.4.3 TWI Pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and

inputs with inputs with spike filtering. When used as GPIO pins or used for other peripherals, the

pins have the same characteristics as other GPIO pins.

3.4.4 GPIO Pins

All the I/O lines integrate a programmable pull-up resistor. Programming of this pull-up resistor is

performed independently for each I/O line through the I/O Controller. After reset, I/O lines default

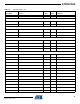

as inputs with pull-up resistors disabled, except when indicated otherwise in the column “Reset

State” of the I/O Controller multiplexing tables.