Datasheet

Table Of Contents

- Small Footprint RMII 10/100 Ethernet Transceiver with HP Auto-MDIX Support

- 1.0 Introduction

- 2.0 Pin Description and Configuration

- 3.0 Functional Description

- 3.1 Transceiver

- 3.2 Auto-negotiation

- 3.3 HP Auto-MDIX Support

- 3.4 MAC Interface

- 3.5 Serial Management Interface (SMI)

- 3.6 Interrupt Management

- 3.7 Configuration Straps

- 3.8 Miscellaneous Functions

- 3.9 Application Diagrams

- 4.0 Register Descriptions

- 4.1 Register Nomenclature

- 4.2 Control and Status Registers

- TABLE 4-2: SMI Register Map

- 4.2.1 Basic Control Register

- 4.2.2 Basic Status Register

- 4.2.3 PHY Identifier 1 Register

- 4.2.4 PHY Identifier 2 Register

- 4.2.5 Auto Negotiation Advertisement Register

- 4.2.6 Auto Negotiation Link Partner Ability Register

- 4.2.7 Auto Negotiation Expansion Register

- 4.2.8 Mode Control/Status Register

- 4.2.9 Special Modes Register

- 4.2.10 Symbol Error Counter Register

- 4.2.11 Special Control/Status Indications Register

- 4.2.12 Interrupt Source Flag Register

- 4.2.13 Interrupt Mask Register

- 4.2.14 PHY Special Control/Status Register

- 5.0 Operational Characteristics

- 6.0 Package Information

- 7.0 Application Notes

- Appendix A: Data Sheet Revision History

- The Microchip Web Site

- Customer Change Notification Service

- Customer Support

- Product Identification System

- Worldwide Sales and Service

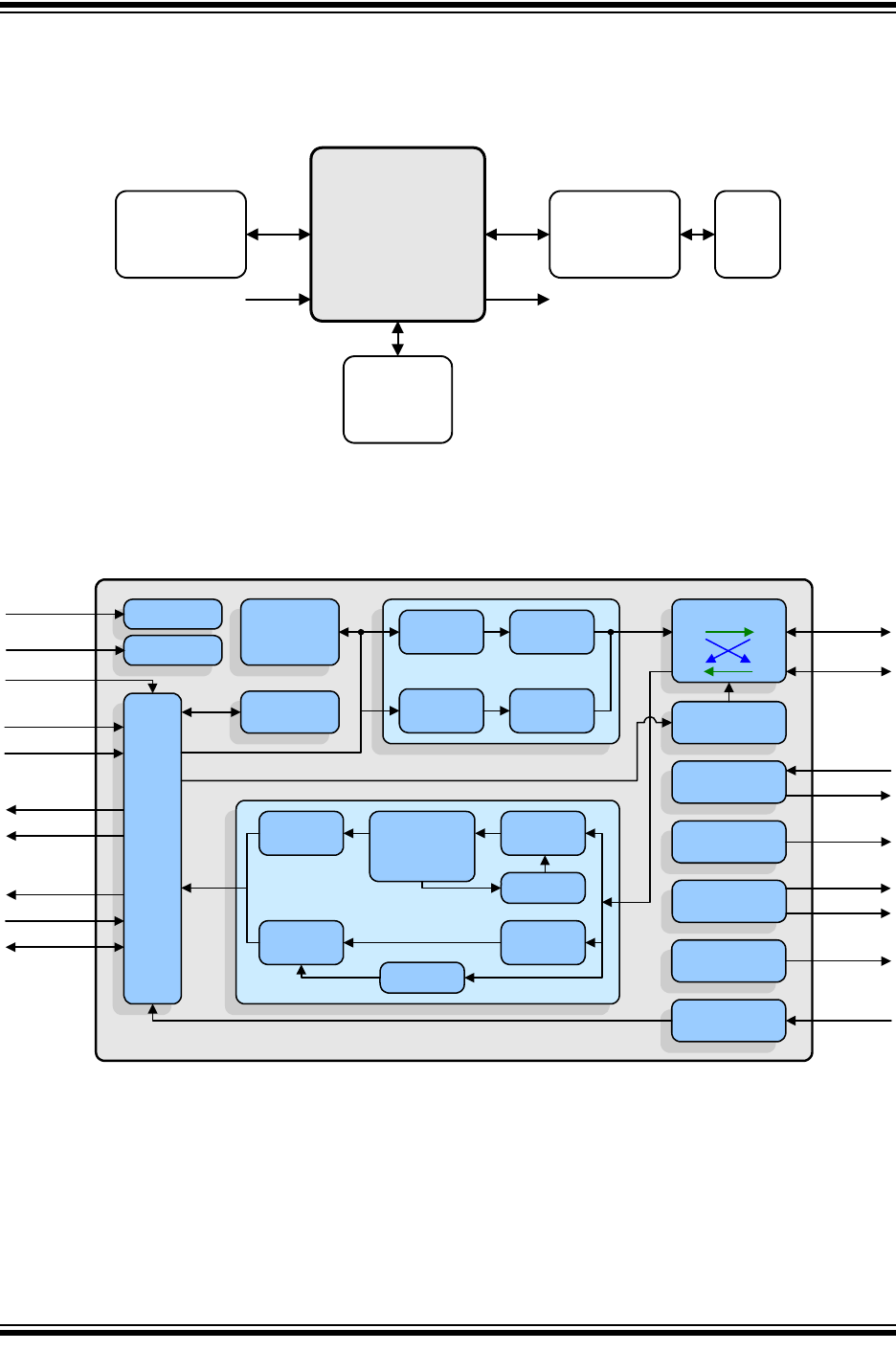

FIGURE 1-1: SYSTEM BLOCK DIAGRAM

LAN8720A/

LAN8720Ai

10/100

Ethernet

MAC

RMII

Mode LED

Transformer

Crystal or

Clock

Oscillator

MDI

RJ45

FIGURE 1-2: ARCHITECTURAL OVERVIEW

RMII Logic

Interrupt

Generator

LEDs

PLL

Receiver

DSP System:

Clock

Data Recovery

Equalizer

Squeltch

& Filters

Analog-to-

Digital

10M RX

Logic

100M RX

Logic

100M PLL

10M PLL

Transmitter

10M

Transmitter

100M

Transmitter

10M TX

Logic

100M TX

Logic

Central Bias

PHY Address

Latches

LAN8720A/LAN8720Ai

RBIAS

LED1

nINT

XTAL2

XTAL1/CLKIN

LED2

Management

Control

Mode Control

Reset Control

MDIX

Control

HP Auto-MDIX

RXP/RXN

TXP/TXN

TXD[0:1]

TXEN

RXD[0:1]

RXER

CRS_DV

MDC

MDIO

Auto-

Negotiation

RMIISEL

nRST

MODE[0:2]

SMI

PHYAD0

2016 Microchip Technology Inc. DS00002165B-page 5

LAN8720A/LAN8720AI