Datasheet

2011-2014 Microchip Technology Inc. DS70000652F-page 61

dsPIC33FJ16(GP/MC)101/102 AND dsPIC33FJ32(GP/MC)101/102/104

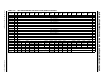

TABLE 4-9: INPUT CAPTURE REGISTER MAP

SFR Name

SFR

Addr

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 All Resets

IC1BUF 0140 Input Capture 1 Register xxxx

IC1CON 0142

— —ICSIDL— — — — — ICTMR ICI1 ICI0 ICOV ICBNE ICM2 ICM1 ICM0 0000

IC2BUF 0144 Input Capture 2 Register xxxx

IC2CON 0146

— —ICSIDL— — — — — ICTMR ICI1 ICI0 ICOV ICBNE ICM2 ICM1 ICM0 0000

IC3BUF 0148 Input Capture 3 Register xxxx

IC3CON 014A

— —ICSIDL— — — — — ICTMR ICI1 ICI0 ICOV ICBNE ICM2 ICM1 ICM0 0000

Legend: x = unknown value on Reset, — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

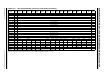

TABLE 4-10: OUTPUT COMPARE REGISTER MAP

SFR Name

SFR

Addr

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

All

Resets

OC1RS 0180 Output Compare 1 Secondary Register xxxx

OC1R 0182 Output Compare 1 Register xxxx

OC1CON 0184

— —OCSIDL— — — — — — — — OCFLT OCTSEL OCM2 OCM1 OCM0 0000

OC2RS 0186 Output Compare 2 Secondary Register xxxx

OC2R 0188 Output Compare 2 Register xxxx

OC2CON 018A

— —OCSIDL— — — — — — — — OCFLT OCTSEL OCM2 OCM1 OCM0 0000

Legend: x = unknown value on Reset, — = unimplemented, read as ‘0’. Reset values are shown in hexadecimal.

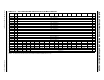

TABLE 4-11: 6-OUTPUT PWM1 REGISTER MAP FOR dsPIC33FJXXMC10X DEVICES

SFR Name

SFR

Addr.

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Reset State

P1TCON 01C0 PTEN —PTSIDL— — — — — PTOPS3 PTOPS2 PTOPS1 PTOPS0 PTCKPS1 PTCKPS0 PTMOD1 PTMOD0

0000 0000 0000 0000

P1TMR 01C2 PTDIR PWM1 Timer Count Value Register

0000 0000 0000 0000

P1TPER 01C4 — PWM1 Time Base Period Register

0111 1111 1111 1111

P1SECMP 01C6 SEVTDIR PWM1 Special Event Compare Register

0000 0000 0000 0000

PWM1CON1 01C8 — — — — — PMOD3 PMOD2 PMOD1 — PEN3H PEN2H PEN1H — PEN3L PEN2L PEN1L

0000 0000 0000 0000

PWM1CON2 01CA — — — — SEVOPS3 SEVOPS2 SEVOPS1 SEVOPS0 — — — — — IUE OSYNC UDIS

0000 0000 0000 0000

P1DTCON1 01CC DTBPS1 DTBPS0 DTB5 DTB4 DTB3 DTB2 DTB1 DTB0 DTAPS1 DTAPS0 DTA5 DTA4 DTA3 DTA2 DTA1 DTA0

0000 0000 0000 0000

P1DTCON2 01CE — — — — — — — — — — DTS3A DTS3I DTS2A DTS2I DTS1A DTS1I

0000 0000 0000 0000

P1FLTACON 01D0 — — FAOV3H FAOV3L FAOV2H FAOV2L FAOV1H FAOV1L FLTAM — — — — FAEN3 FAEN2 FAEN1

0000 0000 0000 0111

P1FLTBCON 01D2 — — FBOV3H FBOV3L FBOV2H FBOV2L FBOV1H FBOV1L FLTBM — — — — FBEN3 FBEN2 FBEN1

0000 0000 0000 0111

P1OVDCON 01D4 — — POVD3H POVD3L POVD2H POVD2L POVD1H POVD1L — — POUT3H POUT3L POUT2H POUT2L POUT1H POUT1L

0011 1111 0000 0000

P1DC1 01D6 PWM1 Duty Cycle 1 Register

0000 0000 0000 0000

P1DC2 01D8 PWM1 Duty Cycle 2 Register

0000 0000 0000 0000

P1DC3 01DA PWM1 Duty Cycle 3 Register

0000 0000 0000 0000

PWM1KEY 01DE PWMKEY<15:0>

0000 0000 0000 0000

Legend:

— = unimplemented, read as ‘

0

’. Reset values are shown in hexadecimal.