Single-Chip Microcontrollers User's Manual

120

CHAPTER 5 CPU ARCHITECTURE

5.3.3 Table indirect addressing

[Function]

Table contents (branch destination address) of the particular location to be addressed by bits 1 to 5 of the

immediate data of an operation code are transferred to the program counter (PC) and branched.

Table indirect addressing is carried out when the CALLT [addr5] instruction is executed. This instruction can

refer to the address stored in the memory table 40H to 7FH and branch to all the memory space.

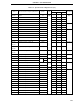

[Illustration]

15 1

15 0

PC

70

Low Addr.

High Addr.

Memory (Table)

Effective Address+1

Effective Address

01

00000000

87

87

65 0

0

111

765 10

ta

4–0

Operation Code