Data Sheet

Table Of Contents

- 1. General description

- 2. Features and benefits

- 3. Ordering information

- 4. Functional diagram

- 5. Pinning information

- 6. Functional description

- 7. Limiting values

- 8. Recommended operating conditions

- 9. Static characteristics

- 10. Dynamic characteristics

- 11. Waveforms

- 12. Package outline

- 13. Abbreviations

- 14. Revision history

- 15. Legal information

- 16. Contact information

- 17. Contents

1. General description

The HEF4011B is a quad 2-input NAND gate. The outputs are fully buffered for the

highest noise immunity and pattern insensitivity to output impedance.

It operates over a recommended V

DD

power supply range of 3 V to 15 V referenced to V

SS

(usually ground). Unused inputs must be connected to V

DD

, V

SS

, or another input.

2. Features and benefits

Fully static operation

5 V, 10 V, and 15 V parametric ratings

Standardized symmetrical output characteristics

Specified from 40 C to +125 C

Complies with JEDEC standard JESD 13-B

Inputs and outputs are protected against electrostatic effects

3. Ordering information

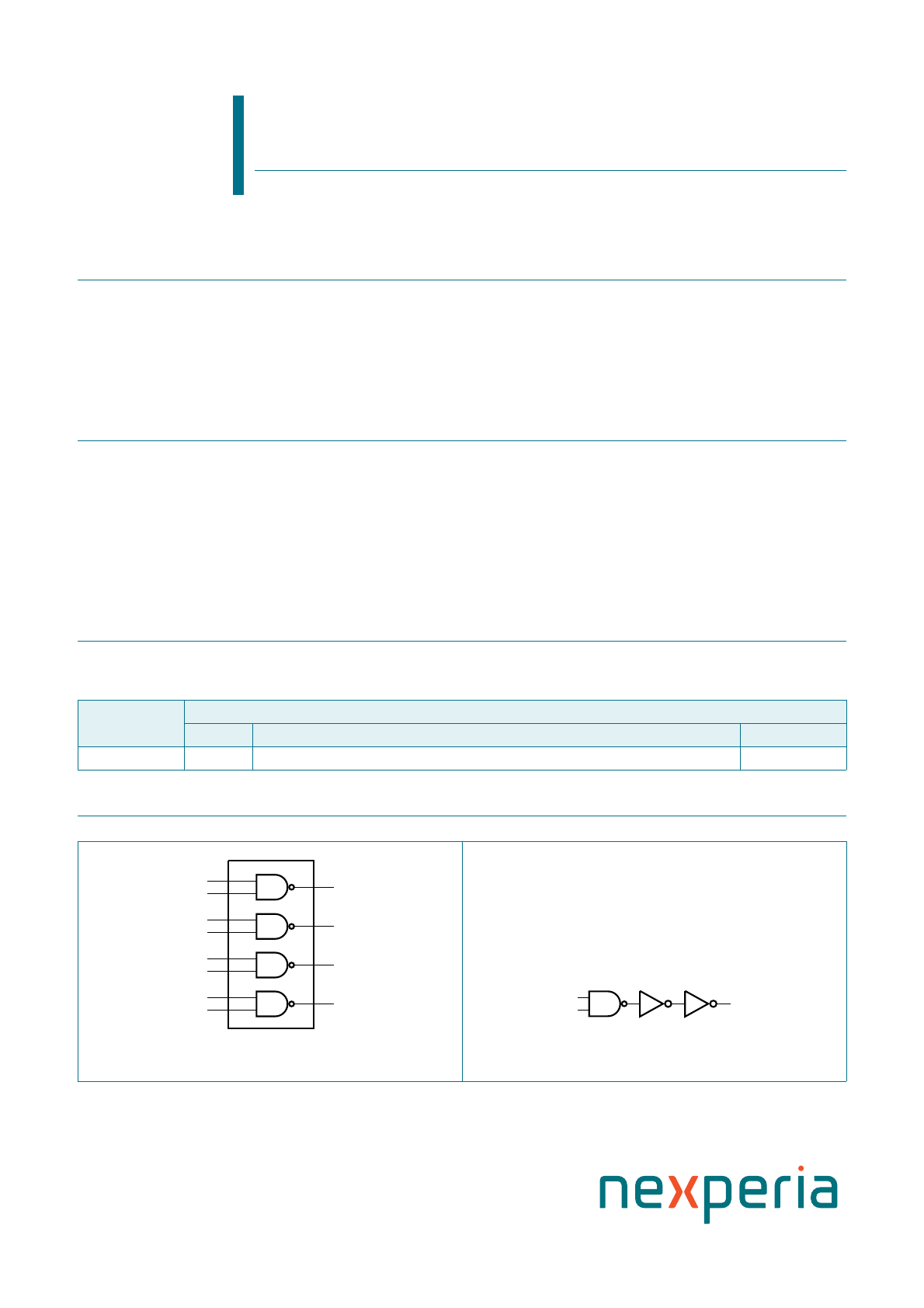

4. Functional diagram

HEF4011B

Quad 2-input NAND gate

Rev. 6 — 10 December 2015 Product data sheet

Table 1. Ordering information

All types operate from

40

C to +125

C

Type number Package

Name Description Version

HEF4011BT SO14 plastic small outline package; 14 leads; body width 3.9 mm SOT108-1

Fig 1. Functional diagram Fig 2. Logic diagram (one gate)

DDQ

%

$

<

%

$

<

%

$

<

%

$

<

DDQ

Q<

Q$

Q%