User Manual

Table Of Contents

Jennic

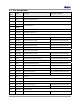

4. Pin Configurations

1

2

3

4

16

ADC4

DAC1

DAC2

COMP+

COMP-

SPICLK

SPIMISO

SPIMOSI

SPISSZ

DIO0/SPISEL1

DIO1/SPISEL2

DIO2/SPISEL3

SPISSM

SPISWP

DIO3/SPISEL4

DIO4/CTS0

DIO5/RTS0

DIO6/TXD0

DIO7/RXD0

DIO8/TIM0GT

DIO9/TIM0_CAP

DIO10/TIM0_OUT

DIO11/TIM1GT

VDD

GND

VSSA

ADC3

ADC2

ADC1

DNC

DNC

DIO20/RXD1

DIO19/TXD1

DIO18/RTS1

DIO17/CTS1

DIO16

DIO15/SIF_D

RESETN

DIO14/SIF_CLK

DIO13/TIM1_OUT

DIO12/TIM1_CAP

5

6

7

8

9

10

11

12

13

14

15

17 18 19 20 21 22 23 24 25 26

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

Antenna

J1

Figure 1: Pin Configuration (top view)

Note that the same basic pin configuration applies for all module designs. However, DIO3/SPISEL4 and

DIO2/SPISEL3 are not available with high power modules.

4 Preliminary - JN-DS-JN5121-xxx-Myy v1.21 © Jennic 2006