User Manual

Table Of Contents

Jennic

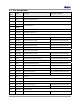

4.1. Pin Assignment

Module

Pin

Signal Function Alternative Function

1 ADC4 Analogue to Digital input

2 DAC1 Digital to Analogue output

3 DAC2 Digital to Analogue output

4 COMP+

5 COMP-

Comparator inputs

6 SPICLK SPI master clock out/slave clock in

7 SPIMISO SPI Master In/Slave Out

8 SPIMOSI SPI Master Out/Slave In

9 SPISSZ SPI select from module - SS0 (output)

10 SPISEL1 SPI Slave Select1 (output) General Purpose Digital I/O DIO0

11 SPISEL2 SPI Slave Select2 (output) General Purpose Digital I/O DIO1

12 SPISEL3* SPI Slave Select3 (output) General Purpose Digital I/O DIO2 *

13 SPISSM SPI select to FLASH (input)

14 SPISWP FLASH write protect (input)

15 SPISEL4*

(t Hi

SPI Slave Select4 (output) General Purpose Digital I/O DIO3*

16 CTS0 UART0 Clear To Send (input) General Purpose Digital I/O DIO4

17 RTS0 UART0 Request To Send (output) General Purpose Digital I/O DIO5

18 TXD0 UART0 Transmit Data (output) General Purpose Digital I/O DIO6

19 RXD0 UART0 Receive Data (input) General Purpose Digital I/O DIO7

20 TIM0GT Timer0 clock/gate (input) General Purpose Digital I/O DIO8

21 TIM0_CAP Timer0 capture (input) General Purpose Digital I/O DIO9

22 TIM0_OUT Timer0 PWM (output) General Purpose Digital I/O DIO10

23 TIM1GT Timer1 clock/gate (input) General Purpose Digital I/O DIO11

24 VDD 3V power

25 GND Digital ground

26 VSSA Analogue ground

27 TIM1_CAP Timer1 capture (input) General Purpose Digital I/O DIO12

28 TIM1_OUT Timer1 PWM (output) General Purpose Digital I/O DIO13

29 RESETN Active low reset

30 SIF_CLK Serial Interface clock / Intelligent peripheral clock General Purpose Digital I/O DIO14

© Jennic 2006 Preliminary - JN-DS-JN5121-xxx-Myy v1.22 5