Datasheet

SCD55100A, SCD55101A, SCD55102A, SCD55103A, SCD55104A

2008-07-22 13

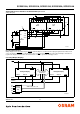

SCD5510XA Interface with Motorola 68HC05C4 Microprocessor

(using SPI port)

Cascading Multiple Displays

Multiple displays can be cascaded using the CLKSEL and CLK I/O pins as shown below. The display designated as the Master Clock

source should have its

CLKSEL pin tied high and the slaves should have their CLKSEL pins tied low. All CLK I/O pins should be tied

together. One display CLK I/O can drive 15 slave CLK I/Os. Use

RST to synchronize all display counters.

Cascading Multiple Displays

IDCD5223

CC

V

40

32

33

10

11

MOSI

SCLK

PA1

PA0

PA2

RST

68HC05C4

OSC2

U1

OSC1

CC

V

20

9

1

39

38

CC

V

16

14

SD

CLK

LOAD

126

139

DATA

SCD

Master

28

27 23 1920

CC

V

TAN

22 µF

SCD

Slave

SD

CLK

1

LOAD

26

DATA

91314

+

2015 28 27 23 19 16 15

0.01 µF

IDCD5030

RST CLK SEL

Intelligent Display

CC

V

DATA SDCLK LOAD

14 more displays

in between

DATA

SDCLK

Decoder

Address

Address Decode 1-14

A0

A1

A3

RST

CLK I/O

Intelligent Display

DATA

RST

SDCLK

CLK I/O

LOAD

CLK SEL

Chip

0

15

A2

LD

CE