User guide

TL/H/10559

ADC1061 10-Bit High-Speed mP-Compatible A/D Converter with Track/Hold Function

December 1994

ADC1061 10-Bit High-Speed mP-Compatible

A/D Converter with Track/Hold Function

General Description

Using a modified half-flash conversion technique, the 10-bit

ADC1061 CMOS analog-to-digital converter offers very fast

conversion times yet dissipates a maximum of only 235 mW.

The ADC1061 performs a 10-bit conversion in two lower-

resolution ‘‘flashes’’, thus yielding a fast A/D without the

cost, power dissipation, and other problems associated with

true flash approaches.

The analog input voltage to the ADC1061 is tracked and

held by an internal sampling circuit. Input signals at frequen-

cies from DC to greater than 160 kHz can therefore be digi-

tized accurately without the need for an external sample-

and-hold circuit.

For ease of interface to microprocessors, the ADC1061 has

been designed to appear as a memory location or I/O port

without the need for external interface logic.

Features

Y

1.8 ms maximum conversion time to 10 bits

Y

Low power dissipation: 235 mW (maximum)

Y

Built-in track-and-hold

Y

No external clock required

Y

Single

a

5V supply

Y

No missing codes over temperature

Applications

Y

Waveform digitizers

Y

Disk drives

Y

Digital signal processor front ends

Y

Mobile telecommunications

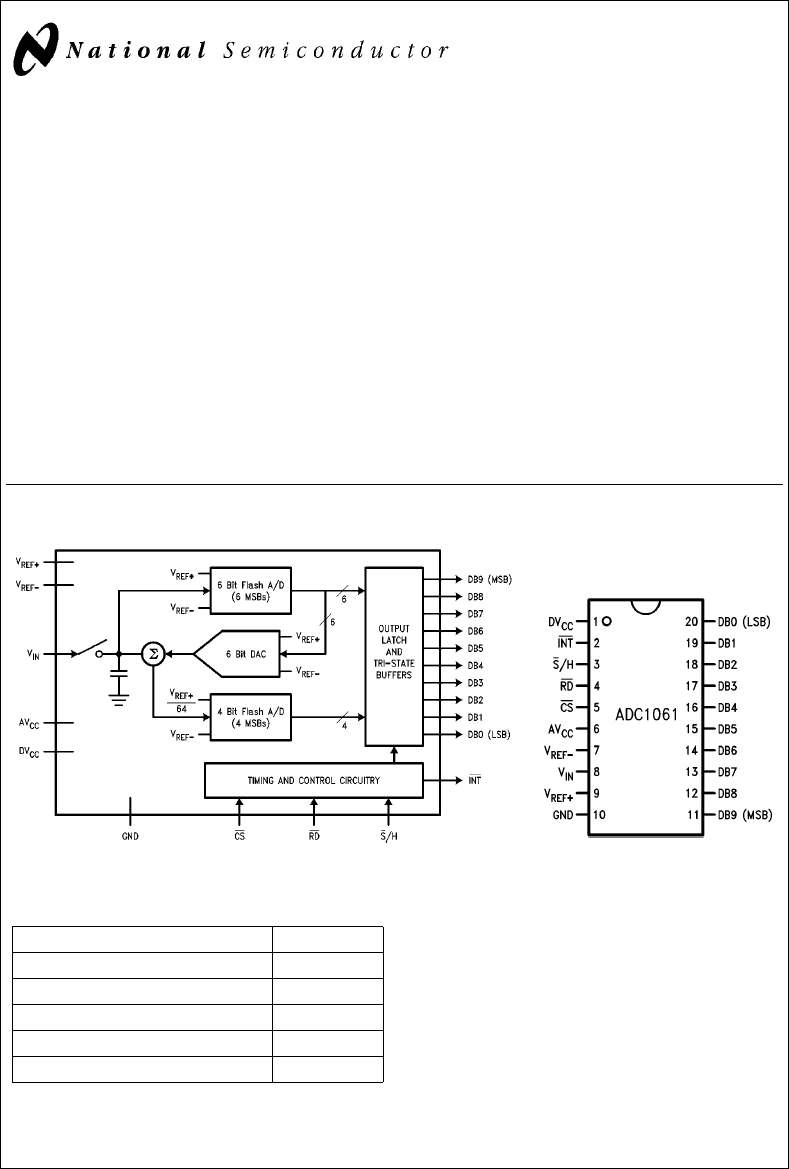

Simplified Block and Connection Diagrams

TL/H/10559–2

Dual-In-Line Package

TL/H/10559–1

Top View

Order Number

ADC1061CIJ, ADC1061CIN,

ADC1061CIWM or ADC1061CMJ

See NS Package J20A,

M20B or N20A

Ordering Information

Industrial (

b

40

§

C

s

T

A

s

85

§

C) Package

ADC1061CIJ J20A

ADC1061CIN N20A

ADC1061CIWM M20B

Military (

b

55

§

C

s

T

A

s

125

§

C) Package

ADC1061CMJ J20A

TRI-STATE

É

is a registered trademark of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M75/Printed in U. S. A.