Instruction Manual

58

AT40K/AT40KLV Series FPGA

0896C–FPGA–04/02

Packaging Information

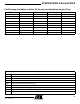

84J – PLCC

1.14(0.045) X 45˚

PIN NO. 1

IDENTIFIER

1.14(0.045) X 45˚

0.51(0.020)MAX

0.318(0.0125)

0.191(0.0075)

A2

2325 Orchard Parkway

San Jose, CA 95131

TITLE

DRAWING NO.

R

REV.

84J, 84-lead, Plastic J-leaded Chip Carrier (PLCC)

B

84J

10/04/01

45˚ MAX (3X)

Notes: 1. This package conforms to JEDEC reference MS-018, Variation AF.

2. Dimensions D1 and E1 do not include mold protrusion.

Allowable protrusion is .010"(0.254 mm) per side. Dimension D1

and E1 include mold mismatch and are measured at the extreme

material condition at the upper or lower parting line.

3. Lead coplanarity is 0.004" (0.102 mm) maximum.

COMMON DIMENSIONS

(Unit of Measure = mm)

SYMBOL

MIN

NOM

MAX

NOTE

A 4.191 – 4.572

A1 2.286 – 3.048

A2 0.508 – –

D 30.099 – 30.353

D1 29.210 – 29.413 Note 2

E 30.099 – 30.353

E1 29.210 – 29.413 Note 2

D2/E2 27.686 – 28.702

B 0.660 – 0.813

B1 0.330 – 0.533

e 1.270 TYP

A

A1

B1

D2/E2

B

e

E1 E

D1

D