Manual

9

6264A–CAP–21-May-07

AT91CAP9S500A/AT91CAP9S250A

LCD Controller - LCDC

LCDD0 - LCDD23 LCD Data Bus Input

LCDVSYNC LCD Vertical Synchronization Output

LCDHSYNC LCD Horizontal Synchronization Output

LCDDOTCK LCD Dot Clock Output

LCDDEN LCD Data Enable Output

LCDCC LCD Contrast Control Output

Ethernet 10/100 E

ETXCK/EREFCK Transmit Clock or Reference Clock Input MII only, REFCK in RMII

ERXCK Receive Clock Input MII only

ETXEN Transmit Enable Output

ETX0-ETX3 Transmit Data Output ETX0-ETX1 only in RMII

ETXER Transmit Coding Error Output MII only

ERXDV Receive Data Valid Input

RXDV in MII, CRSDV in

RMII

ERX0-ERX3 Receive Data Input ERX0-ERX1 only in RMII

ERXER Receive Error Input

ECRS Carrier Sense and Data Valid Input MII only

ECOL Collision Detect Input MII only

EMDC Management Data Clock Output

EMDIO Management Data Input/Output I/O

EF100 Force 100Mbit/sec. Output High RMII only

USB High Speed Device

FSDM USB Full Speed Data - Analog

FSDP USB Full Speed Data + Analog

HSDM USB High Speed Data - Analog

HSDP USB High Speed Data + Analog

VBG Bias Voltage Reference Analog

PLLRCU USB PLL Test Pad Analog

OHCI USB Host Port

HDPA USB Host Port A Data + Analog

HDMA USB Host Port A Data - Analog

HDPB USB Host Port B Data + Analog

HDMB USB Host Port B Data - Analog

ADC

AD0-AD7 Analog Inputs Analog

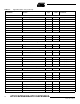

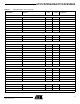

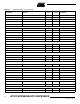

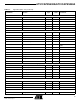

Table 3-1. Signal Description List (Continued)

Signal Name Function Type

Active

Level Comments