Instruction Manual

Table Of Contents

- 1769-UM006E-EN-P, Compact High-speed Counter Module User Manual

- Summary of Changes

- Table of Contents

- Preface

- 1 - Module Overview

- 2 - Module Operation

- 3 - Installation and Wiring

- 4 - Module Configuration, Output, and Input Data

- Configure the Module

- Configuration Array

- General Configuration Bits

- Filter Selection

- Program Mode and Program State Run

- Output Program Value (Out0ProgramValue through Out3ProgramValue)

- Output Fault Mode and Output Fault State Run

- Output Fault Value (Out0FaultValue through Out3FaultValue)

- Counter Maximum Count (CtrnMaxCount)

- Counter Minimum Count (CtrnMinCount)

- Counter Preset (CtrnPreset)

- Counter Hysteresis (CtrnHysteresis)

- Counter Scalar (CtrnScalar)

- Cyclic Rate Update Time (CtrnCyclicRateUpdateTime)

- Configuration Flags

- Range High Limit (Range0To11[n].HighLimit) and Range Low Limit (Range0To11[n].LowLimit)

- Range Output Control (Range0To11[n].OutputControl)

- Range Configuration Flags

- Output Array

- Output on Mask (OutputOnMask.0 through OutputOnMask.15)

- Output Off Mask (OutputOffMask.0 through OutputOffMask.15)

- Range Enable (RangeEn.0 through RangeEn.15)

- RBF - Reset Blown Fuse (ResetBlownFuse)

- Control Bits

- Range High Limit or Direct Write Value (Range12To15[n].HiLimOrDirWr)

- Range Low Limit (Range12To15[n].LowLimit)

- Range Output Control (Range12To15[n].OutputControl)

- Range Configuration Flags (12To15)

- Input Array

- Input State (InputStateA0 through InputStateZ1)

- Readback (Readback.0 through Readback.15)

- Status Flags

- Range Active (RangeActive.0 through RangeActive.15)

- Current Count (Ctr[n].CurrentCount)

- Stored Count (Ctr[n].StoredCount)

- Current Rate (Ctr[0].CurrentRate to Ctr[3].CurrentRate)

- Pulse Interval (Ctr[0].PulseInterval and Ctr[1].PulseInterval)

- Status Flags

- 5 - Diagnostics and Troubleshooting

- A - Specifications

- B - Program a 1769-HSC Module, CompactLogix Controller, and 845F Incremental Encoder with RSLogix 5000 Software

- C - Program a 1769-HSC Module, MicroLogix 1500 Controller, and 845F Incremental Encoder with RSLogix 500 Software

- D - Programming Quick Reference

- E - History of Changes

- Glossary

- Index

- Back Cover

Rockwell Automation Publication 1769-UM006E-EN-P - July 2013 91

Module Configuration, Output, and Input Data Chapter 4

Output on Mask (OutputOnMask.0 through OutputOnMask.15)

This word lets you turn on any output, real or virtual, when the corresponding bit

is set. This mask is logically ORed with the range masks but logically ANDed

with the Output Off Mask Word described on

page 91.

Using the Output On Mask, all of the module’s outputs can be turned on directly

by the user control program, like discrete outputs. A bit which is set in the mask

turns on the corresponding real or virtual output.

See

Output Control on page 36 and Output Control Example on page 43 for

more information about output determination.

Output Off Mask (OutputOffMask.0 through OutputOffMask.15)

This word turns OFF any output, real or virtual, when the corresponding bit is

reset. This mask has veto power over all the Range masks and the Output On

Mask described above. It is logically AND’ed with the results of those masks.

See

Output Control on page 36 and Output Control Example on page 43 for

more information about output determination.

Range Enable (RangeEn.0 through RangeEn.15)

When the bit corresponding to the range number is set,

Range[n].OutputControl is applied whenever the range is active.

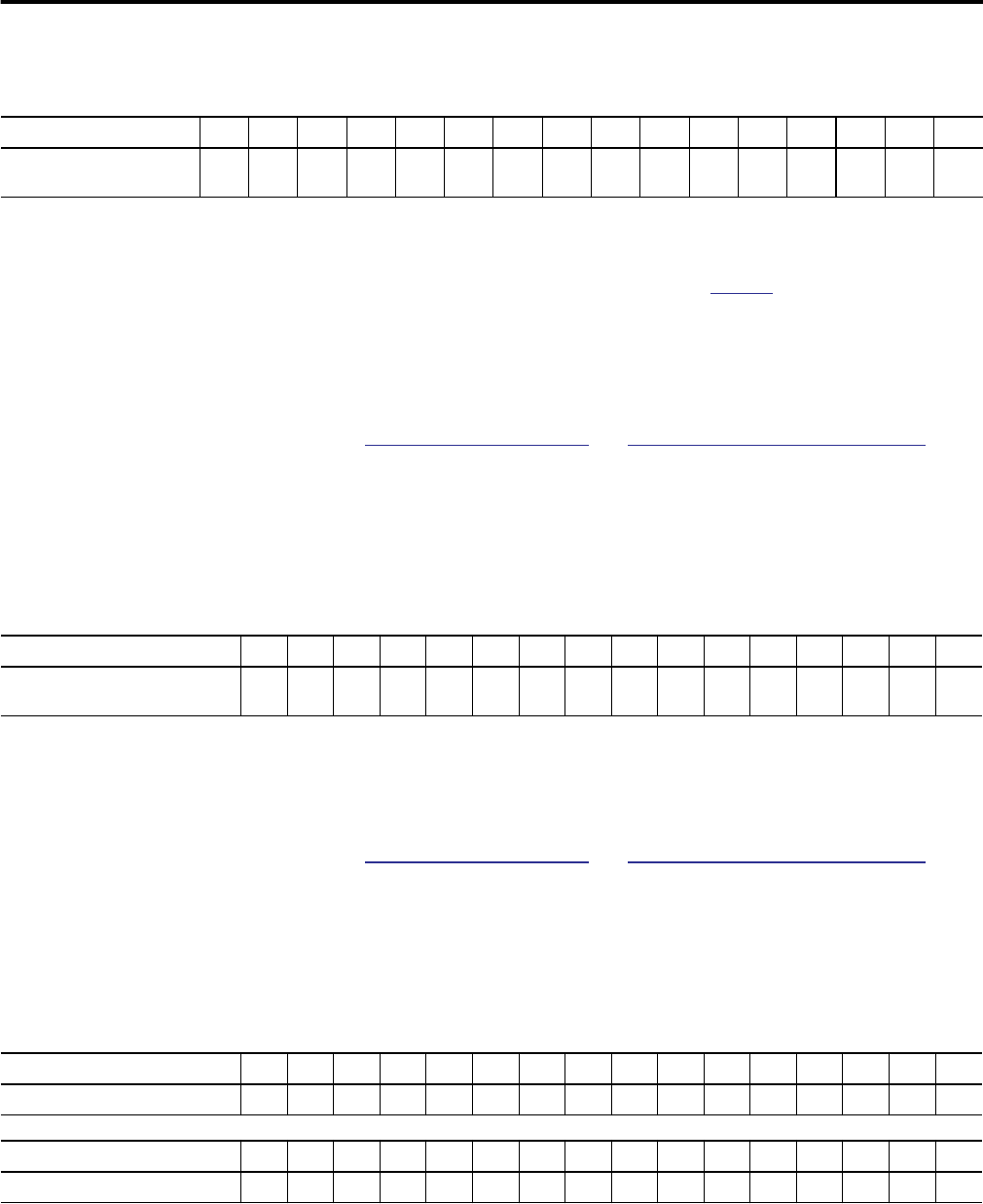

Output Array Word 0 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Output On Mask Out

15

Out

14

Out

13

Out

12

Out

11

Out

10

Out

9

Out

8

Out

7

Out

6

Out

5

Out

4

Out

3

Out

2

Out

1

Out

0

TIP

The corresponding Output Off Mask bit must be set to enable this bit.

Output Array Word 1 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Output Off Mask Out

15

Out

14

Out

13

Out

12

Out

11

Out

10

Out

9

Out

8

Out

7

Out

6

Out

5

Out

4

Out

3

Out

2

Out

1

Out

0

TIP

This mask can be overridden when a safe state is indicated.

Output Array Word 2 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Range Enable R15 R14 R13 R12 R11 R10 R9 R8 R7 R6 R5 R4 R3 R2 R1 R0

Output Array Word 2 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Range Enable R3 R2 R1 R0