Specifications

About This Book

MPC8555E Configurable Development System Reference Manual, Rev. 1

Freescale Semiconductor xv

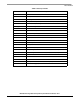

Table i. Glossary of Terms

Term Description

ATM Asynchronous transfer mode

CARRIER HIP-compliant HIPcard such as CDS, Elysium, etc.

CDC CPU daughtercard

CDS Configurable development system; customer development system

CPM Communications processing machine

Daughtercard CPU-specific daughtercard which connects to a carrier board

DDR Double-data rate

GMII Gigabit media-independent interface

HIP Hardware interoperability platform

IOCARD IO breakout card for a carrier board

LB Local bus (that is, Flash/SRAM/SDRAM interface)

MAC Media access control

MII Media-independent interface

Motherboard HIP-compliant motherboard such as Arcadia, etc.

OUI Organizationally unique identifier

PC-1600 DDR providing 1600 MB/s bandwidth (@8 bytes/clk = 200 MHz)

PC-2100 DDR providing 2100 MB/s bandwidth (@8 bytes/clk = 266 MHz)

PHY Physical interface

PM Performance monitor

RIO RapidIO

TSEC Triple-speed Ethernet controller (10/100/1G speeds)

TWG Technical working group