Product Specs

Table Of Contents

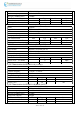

第

11

页 共

15

页

5

VDD33

3.3V

6

GND

Ground

7

NFC_RF_DIS

NC

8

NFC_INT

NC

9

NFC_CLK

NC

10

NFC_DATA

NC

11

COEX_RXD

GPIO6

12

COEX_TXD

GPIO12

13

COEX3

GPIO7

14~16

NC

NC

17

GND

Ground

18~19

NC

NC

20

GND

Ground

21~22

NC

NC

23

GND

Ground

24

HST_WAKE_DEV

GPIO13

25

NC

NC

26

GND

Ground

27

SUSCLK

Shared with EECS. External 32K or RTC clock input

28

WL_DIS_N

GPIO9

G2

GND

Ground

29

WAKE_N

WAKE_N

30

CLKREQ

CLKREQ

31

PERSTB

PCI Express Reset Signal: active low.

When the PERST# is asserted at power-on state, the RTL8821CE

returns to a pre-defined reset state and is ready for initialization and

configuration after the de-assertion of the PERST#.

32

GND

Ground

33

REFCLK_N

PCI Express Differential Reference Clock Source: 100MHz±300ppm

34

REFCLK_P

PCI Express Differential Reference Clock Source: 100MHz±300ppm