Car Stereo System - Car Radio Digital Signal Processor User Manual

www.ti.com

SM320C6455-EP

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS462B – SEPTEMBER 2007 – REVISED JANUARY 2008

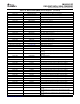

Table 7-71. Ethernet MAC (EMAC) Control Registers (continued)

HEX ADDRESS RANGE ACRONYM REGISTER NAME

02C8 0158 RX6FREEBUFFER Receive Channel 6 Free Buffer Count Register

02C8 015C RX7FREEBUFFER Receive Channel 7 Free Buffer Count Register

02C8 0160 MACCONTROL MAC Control Register

02C8 0164 MACSTATUS MAC Status Register

02C8 0168 EMCONTROL Emulation Control Register

02C8 016C FIFOCONTROL FIFO Control Register (Transmit and Receive)

02C8 0170 MACCONFIG MAC Configuration Register

02C8 0174 SOFTRESET Soft Reset Register

02C8 0178 - 02C8 01CC - Reserved

02C8 01D0 MACSRCADDRLO MAC Source Address Low Bytes Register (Lower 32 bits)

02C8 01D4 MACSRCADDRHI MAC Source Address High Bytes Register (Upper 32 bits)

02C8 01D8 MACHASH1 MAC Hash Address Register 1

02C8 01DC MACHASH2 MAC Hash Address Register 2

02C8 01E0 BOFFTEST Back Off Test Register

02C8 01E4 TPACETEST Transmit Pacing Algorithm Test Register

02C8 01E8 RXPAUSE Receive Pause Timer Register

02C8 01EC TXPAUSE Transmit Pause Timer Register

02C8 01F0 - 02C8 01FC - Reserved

02C8 0200 - 02C8 02FC (see Table 7-72 ) EMAC Statistics Registers

02C8 0300 - 02C8 03FC - Reserved

02C8 0400 - 02C8 04FC - Reserved

MAC Address Low Bytes Register (used in receive address

02C8 0500 MACADDRLO

matching)

MAC Address High Bytes Register (used in receive address

02C8 0504 MACADDRHI

matching)

02C8 0508 MACINDEX MAC Index Register

02C8 050C - 02C8 05FC - Reserved

02C8 0600 TX0HDP Transmit Channel 0 DMA Head Descriptor Pointer Register

02C8 0604 TX1HDP Transmit Channel 1 DMA Head Descriptor Pointer Register

02C8 0608 TX2HDP Transmit Channel 2 DMA Head Descriptor Pointer Register

02C8 060C TX3HDP Transmit Channel 3 DMA Head Descriptor Pointer Register

02C8 0610 TX4HDP Transmit Channel 4 DMA Head Descriptor Pointer Register

02C8 0614 TX5HDP Transmit Channel 5 DMA Head Descriptor Pointer Register

02C8 0618 TX6HDP Transmit Channel 6 DMA Head Descriptor Pointer Register

02C8 061C TX7HDP Transmit Channel 7 DMA Head Descriptor Pointer Register

02C8 0620 RX0HDP Receive Channel 0 DMA Head Descriptor Pointer Register

02C8 0624 RX1HDP Receive Channel 1 DMA Head Descriptor Pointer Register

02C8 0628 RX2HDP Receive Channel 2 DMA Head Descriptor Pointer Register

02C8 062C RX3HDP Receive Channel 3 DMA Head Descriptor Pointer Register

02C8 0630 RX4HDP Receive Channel 4 DMA Head Descriptor Pointer Register

02C8 0634 RX5HDP Receive Channel 5 DMA Head Descriptor Pointer Register

02C8 0638 RX6HDP Receive Channel 6 DMA Head Descriptor Pointer Register

02C8 063C RX7HDP Receive Channel 7 DMA Head Descriptor Pointer Register

Transmit Channel 0 Completion Pointer (Interrupt Acknowledge)

02C8 0640 TX0CP

Register

Transmit Channel 1 Completion Pointer (Interrupt Acknowledge)

02C8 0644 TX1CP

Register

Transmit Channel 2 Completion Pointer (Interrupt Acknowledge)

02C8 0648 TX2CP

Register

Submit Documentation Feedback C64x+ Peripheral Information and Electrical Specifications 205