Car Stereo System - Car Radio Digital Signal Processor User Manual

www.ti.com

7.19 UTOPIA

7.19.1 UTOPIA Device-Specific Information

7.19.2 UTOPIA Peripheral Register Description(s)

SM320C6455-EP

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS462B – SEPTEMBER 2007 – REVISED JANUARY 2008

The Universal Test and Operations PHY Interface for ATM (UTOPIA) peripheral is a 50 MHz, 8 Bit

Slave-only interface. The UTOPIA is more simplistic than the Ethernet MAC, in that the UTOPIA is

serviced directly by the EDMA3 controller. The UTOPIA peripheral contains two, two-cell FIFOs, one for

transmit and one for receive, with which to buffer up data sent/received across the pins. There is a

transmit and a receive event to the EDMA3 channel controller to enable servicing.

For more detailed information on the UTOPIA peripheral, see the TMS320C645x DSP Universal Test and

Operations PHY Interface for ATM 2 (UTOPIA2) User's Guide (literature number SPRUE48 ).

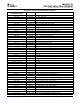

Table 7-104. UTOPIA Registers

HEX ADDRESS RANGE ACRONYM REGISTER NAME

02B4 0000 UCR UTOPIA Control Register

02B4 0004 - Reserved

02B4 0008 - Reserved

02B4 000C - Reserved

02B4 0010 - Reserved

02B4 0014 CDR Clock Detect Register

02B4 0018 EIER Error Interrupt Enable Register

02B4 001C EIPR Error Interrupt Pending Register

02B4 0020 - 02B4 01FF - Reserved

02B4 0200 - 02B7 FFFF - Reserved

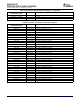

Table 7-105. UTOPIA Data Queues (Receive and Transmit) Registers

HEX ADDRESS RANGE ACRONYM REGISTER NAME

3C00 0000 - 3C00 03FF URQ UTOPIA Receive (Rx) Data Queue

3C00 0400 - 3C00 07FF UXQ UTOPIA Transmit (Tx) Data Queue

C64x+ Peripheral Information and Electrical Specifications230 Submit Documentation Feedback