Car Stereo System - Car Radio Digital Signal Processor User Manual

www.ti.com

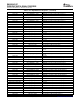

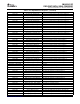

P47 P48 H1

N 0x1F N 0x1F N + 1 0x1F

N N

10

8

4

3

2

1

UXCLK

UXDATA[7:0]

UXADDR[4:0]

UXCLAV

UXENB

UXSOC

9

P46P45

0 x1F

A. The UTOPIA Slave module has signals that are middle-level signals indicating a high-impedance state (i.e., the UXCLAV and UXSOC signals).

5

6

7

SM320C6455-EP

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS462B – SEPTEMBER 2007 – REVISED JANUARY 2008

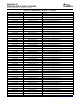

Table 7-108. Timing Requirements for UTOPIA Slave Transmit (see Figure 7-76 )

-720

-850

A-1000/-1000

NO. UNIT

-1200

MIN MAX

2 t

su(UXAV-UXCH)

Setup time, UXADDR valid before UXCLK high 4 ns

3 t

h(UXCH-UXAV)

Hold time, UXADDR valid after UXCLK high 1 ns

8 t

su(UXENBL-UXCH)

Setup time, UXENB low before UXCLK high 4 ns

9 t

h(UXCH-UXENBL)

Hold time, UXENB low after UXCLK high 1 ns

Table 7-109. Switching Characteristics Over Recommended Operating Conditions for UTOPIA Slave

Transmit Cycles (see Figure 7-76 )

-720

-850

A-1000/-1000

NO. PARAMETER UNIT

-1200

MIN MAX

1 t

d(UXCH-UXDV)

Delay time, UXCLK high to UXDATA valid 3 12 ns

4 t

d(UXCH-UXCLAV)

Delay time, UXCLK high to UXCLAV driven active value 3 12 ns

5 t

d(UXCH-UXCLAVL)

Delay time, UXCLK high to UXCLAV driven inactive low 3 12 ns

6 t

d(UXCH-UXCLAVHZ)

Delay time, UXCLK high to UXCLAV going Hi-Z 9 18.5 ns

7 t

w(UXCLAVL-UXCLAVHZ)

Pulse duration (low), UXCLAV low to UXCLAV Hi-Z 3 ns

10 t

d(UXCH-UXSV)

Delay time, UXCLK high to UXSOC valid 3 12 ns

Figure 7-76. UTOPIA Slave Transmit Timing

(A)

232 C64x+ Peripheral Information and Electrical Specifications Submit Documentation Feedback