Datasheet

SLLS037C − MARCH 1988 − REVISED JANUARY 2006

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D Programmable Baud Rate Generator Allows

Division of Any Input Reference Clock by 1

to (2

16

−1) and Generates an Internal 16×

Clock

D Full Double Buffering Eliminates the Need

for Precise Synchronization

D Standard Asynchronous Communication

Bits (Start, Stop, and Parity) Added or

Deleted to or From the Serial Data Stream

D Independent Receiver Clock Input

D Transmit, Receive, Line Status, and Data

Set Interrupts Independently Controlled

D Fully Programmable Serial Interface

Characteristics:

− 5-, 6-, 7-, or 8-Bit Characters

− Even-, Odd-, or No-Parity Bit Generation

and Detection

− 1-, 1 1/2-, or 2-Stop Bit Generation

− Baud Generation (dc to 256 Kbit/s)

D False Start Bit Detection

D Complete Status Reporting Capabilities

D 3-State TTL Drive Capabilities for

Bidirectional Data Bus and Control Bus

D Line Break Generation and Detection

D Internal Diagnostic Capabilities:

− Loopback Controls for Communications

Link Fault Isolation

− Break, Parity, Overrun, Framing Error

Simulation

D Fully Prioritized Interrupt System Controls

D Modem Control Functions (CTS, RTS, DSR,

DTR

, RI, and DCD)

D Easily Interfaces to Most Popular

Microprocessors

D Faster Plug-In Replacement for National

Semiconductor NS16C450

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications o

f

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

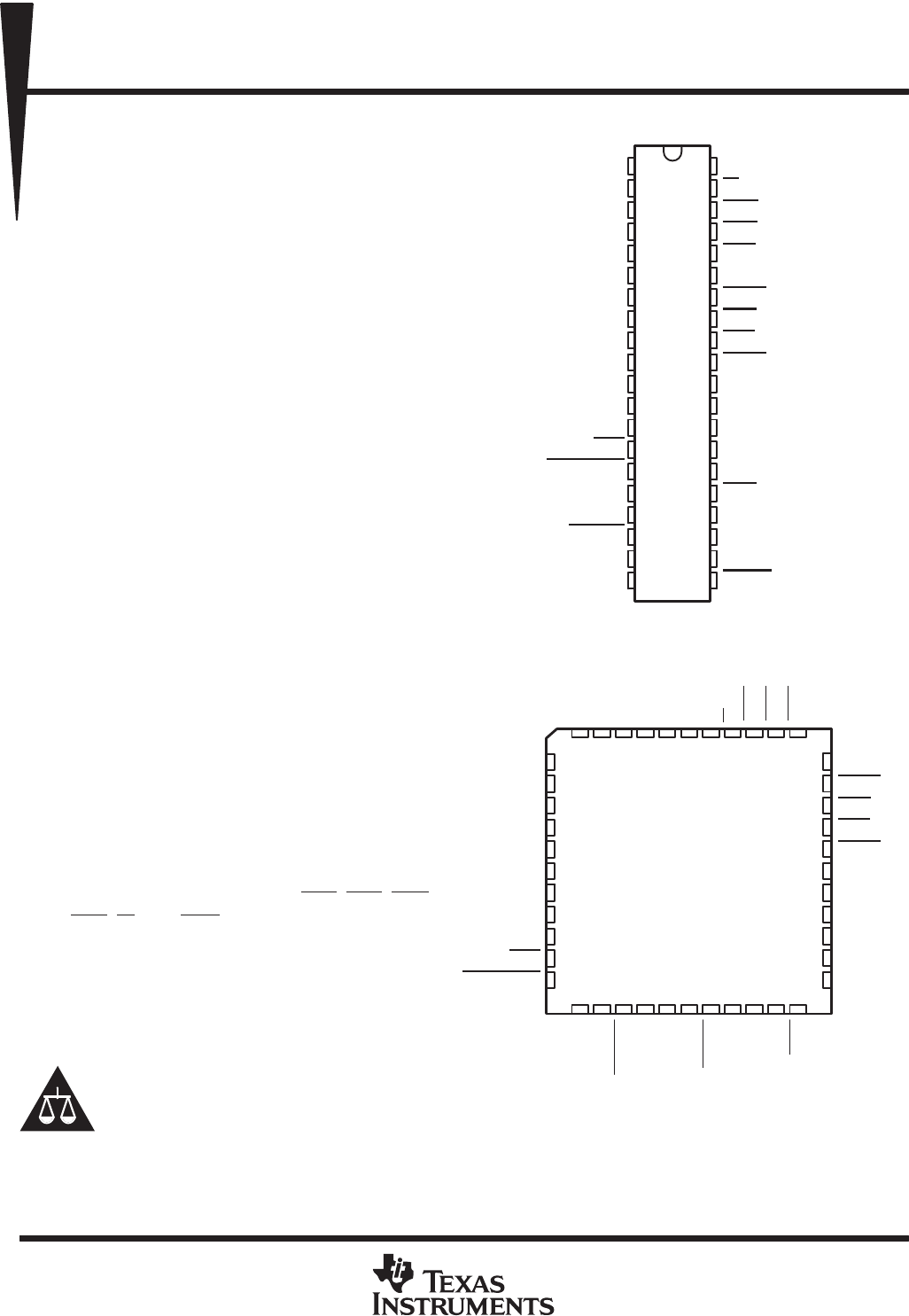

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

D0

D1

D2

D3

D4

D5

D6

D7

RCLK

SIN

SOUT

CS0

CS1

CS2

BAUDOUT

XTAL1

XTAL2

DOSTR

DOSTR

V

SS

V

CC

RI

DCD

DSR

CTS

MR

OUT1

DTR

RTS

OUT2

INTRPT

NC

A0

A1

A2

ADS

CSOUT

DDIS

DISTR

DISTR

N PACKAGE

(TOP VIEW)

MR

OUT1

DTR

RTS

OUT2

NC

INTRPT

NC

A0

A1

A2

39

38

37

36

35

34

33

32

31

30

29

18 19

7

8

9

10

11

12

13

14

15

16

17

D5

D6

D7

RCLK

SIN

NC

SOUT

CS0

CS1

CS2

BAUDOUT

20 21 22 23

FN PACKAGE

(TOP VIEW)

RI

DCD

DSR

CTS

54 321644

D4

D3

D2

D1

D0

NC

DISTR

DDIS

CSOUT

ADS

XTAL1

XTAL2

DOSTR

DOSTR

NC

DISTR

42 41 4043

24 25 26 27 28

NC − No internal connection

V

CC

V

SS

NOTE: 40-pin DIP (N package) will be obsoleted as of 7/30/2006. Please

contact your local distributor or TI Sales Office for more information.

!" #!$% &"'

&! #" #" (" " ") !"

&& *+' &! #", &" ""%+ %!&"

", %% #""'

Copyright 1988 − 2006, Texas Instruments Incorporated