Digital Media System-on-Chip (DMSoC) Product Preview

www.ti.com

PRODUCT PREVIEW

TMS320DM355

Digital Media System-on-Chip (DMSoC)

SPRS463A – SEPTEMBER 2007 – REVISED SEPTEMBER 2007

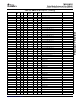

Table 2-23. DM355 Pin Descriptions (continued)

Name BGA Type Group Power PU Reset Description

(4)

Mux Control

ID

(1)

Supply

(2)

PD

(3)

State

SPI0_SDO B11 I/O SPI0 V

DD

in SPI0: Data Out

ASP1_DX C18 I/O ASP5 V

DD

in ASP1: Transmit Data

121

ASP1_CLKX D19 I/O ASP5 V

DD

in ASP1: Transmit Clock

121

ASP1_FSX E16 I/O ASP5 V

DD

in ASP1: Transmit Frame Sync

121

ASP1_DR C19 I/O ASP5 V

DD

in ASP1: Receive Data

121

ASP1_CLKR D18 I/O ASP5 V

DD

in ASP1: Receive Clock

121

ASP1_FSR E17 I/O ASP5 V

DD

in ASP1: Receive Frame Synch

121

ASP1_CLKS D17 I ASP5 V

DD

in ASP1: Master Clock

121

RESET D11 I V

DD

PU in Global Chip Reset (active low)

MXI1 A9 I Clocks V

DD

in Crystal input for system oscillator (24 MHz)

MXO1 B9 O Clocks V

DD

out Output for system oscillator (24 MHz)

MXI2 R1 I Clocks V

DD

in Crystal input for video oscillator (27 MHz).

This crystal is not required

V

DD

MXO2 T1 O Clocks V

DD

out Output for video oscillator (27 MHz). This

crystal is not required.

V

DD

TCK E10 I EMUL V

DD

PU in JTAG test clock input

ATIO

N

TDI D9 I EMUL V

DD

PU in JTAG test data input

ATIO

N

TDO E9 O EMUL V

DD

out L JTAG test data output

ATIO

N

TMS D8 I EMUL V

DD

PU in JTAG test mode select

ATIO

N

TRST C9 I EMUL V

DD

PD in JTAG test logic reset (active low)

ATIO

N

RTCK E11 O EMUL V

DD

out L JTAG test clock output

ATIO

N

EMU0 E8 I/O EMUL V

DD

PU in JTAG emulation 0 I/O

ATIO

V

DD

N

V

DD

EMU1 E7 I/O EMUL V

DD

PU in JTAG emulation 1 I/O

ATIO

EMU[1:0] = 00 - Force Debug Scan chain

N

(ARM and ARM ETB TAPs connected)

EMU[1:0] = 11 - Normal Scan chain (ICEpick

only)

RSV01 J1 A Reserved. This signal should be left as a No

I/O/Z Connect or connected to V

SS

.

RSV02 K1 A Reserved. This signal should be left as a No

I/O/Z Connect or connected to V

SS

.

Submit Documentation Feedback Device Overview 51