- TVP5147M1PFP NTSC/PAL/SECAM 2x10-Bit Digital Video Decoder (Rev. A

Functional Description

64

SLES140A—March 2007TVP5147M1PFP

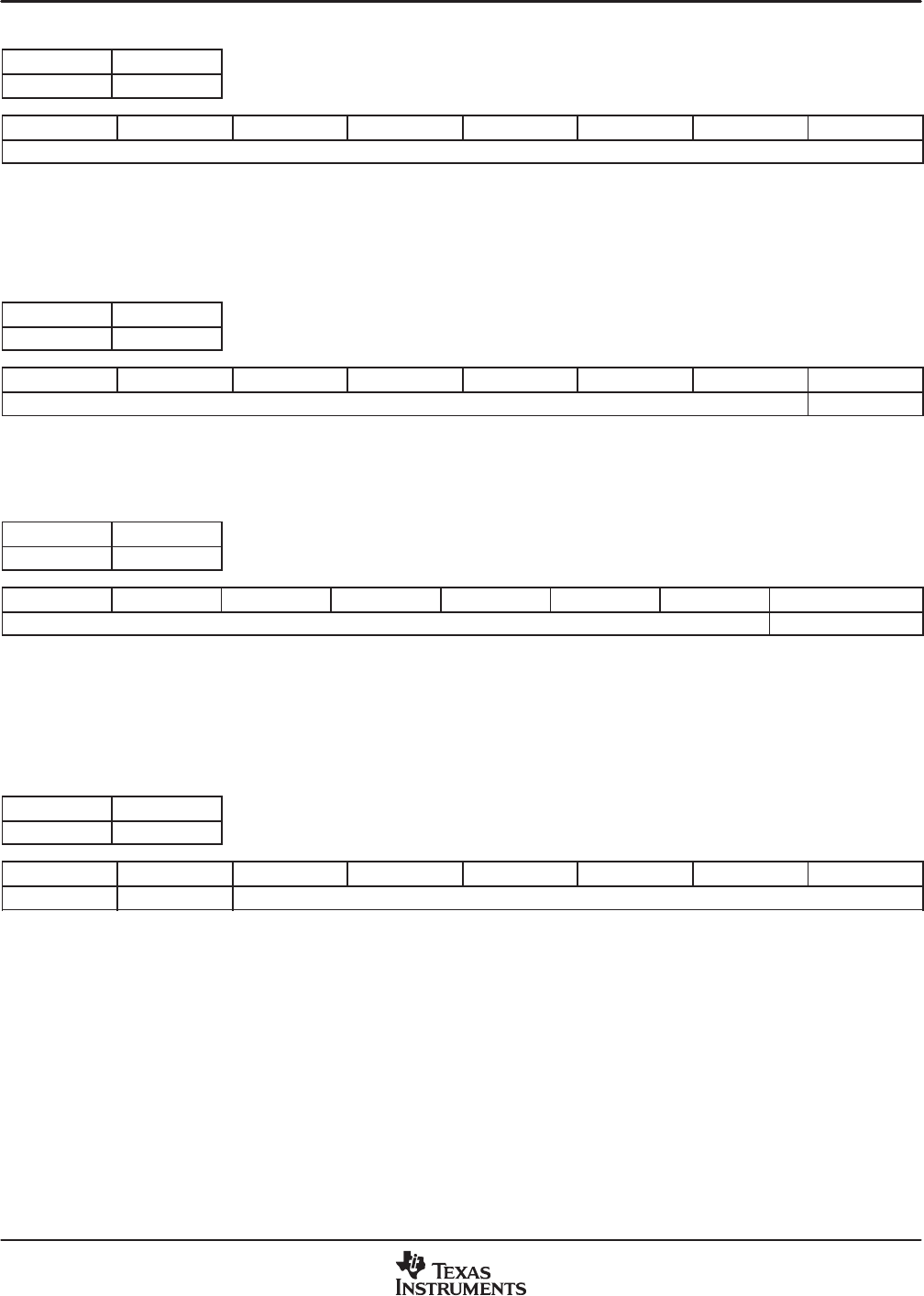

2.11.69 VDP FIFO Interrupt Threshold Register

Subaddress BDh

Default 80h

7 6 5 4 3 2 1 0

Threshold [7:0]

Threshold [7:0]: This register is programmed to trigger an interrupt when the number of words in the FIFO

exceeds this value.

NOTE: 1 word equals 2 bytes.

2.11.70 VDP FIFO Reset Register

Subaddress BFh

Default 00h

7 6 5 4 3 2 1 0

Reserved FIFO reset

FIFO reset: Writing any data to this register clears the FIFO and VDP data register (CC, WSS, VITC and VPS).

After clearing, this register is automatically cleared.

2.11.71 VDP FIFO Output Control Register

Subaddress C0h

Default 00h

7 6 5 4 3 2 1 0

Reserved Host access enable

Host access enable: This register is programmed to allow the host port access to the FIFO or to allow all VDP

data to go out the video output.

0 = Output FIFO data to the video output Y[9:2] (default)

1 = Allow host port access to the FIFO data

2.11.72 VDP Line Number Interrupt Register

Subaddress C1h

Default 00h

7 6 5 4 3 2 1 0

Field 1 enable Field 2 enable Line number [5:0]

Field 1 interrupt enable:

0 = Disabled (default)

1 = Enabled

Field 2 interrupt enable:

0 = Disabled (default)

1 = Enabled

Line number [5:0]: Interrupt line number (default 00h)

This register is programmed to trigger an interrupt when the video line number exceeds this value in bits [5:0].

This interrupt must be enabled at address F4h.

NOTE: The line number value of 0 or 1 is invalid and does not generate an interrupt.