Flash Memory Card Datasheet

T

T

T

S

S

S

1

1

1

6

6

6

G

G

G

~

~

~

6

6

6

4

4

4

G

G

G

C

C

C

F

F

F

4

4

4

0

0

0

0

0

0

400X CompactFlash Card

Transcend Information Inc.

V1.0

12

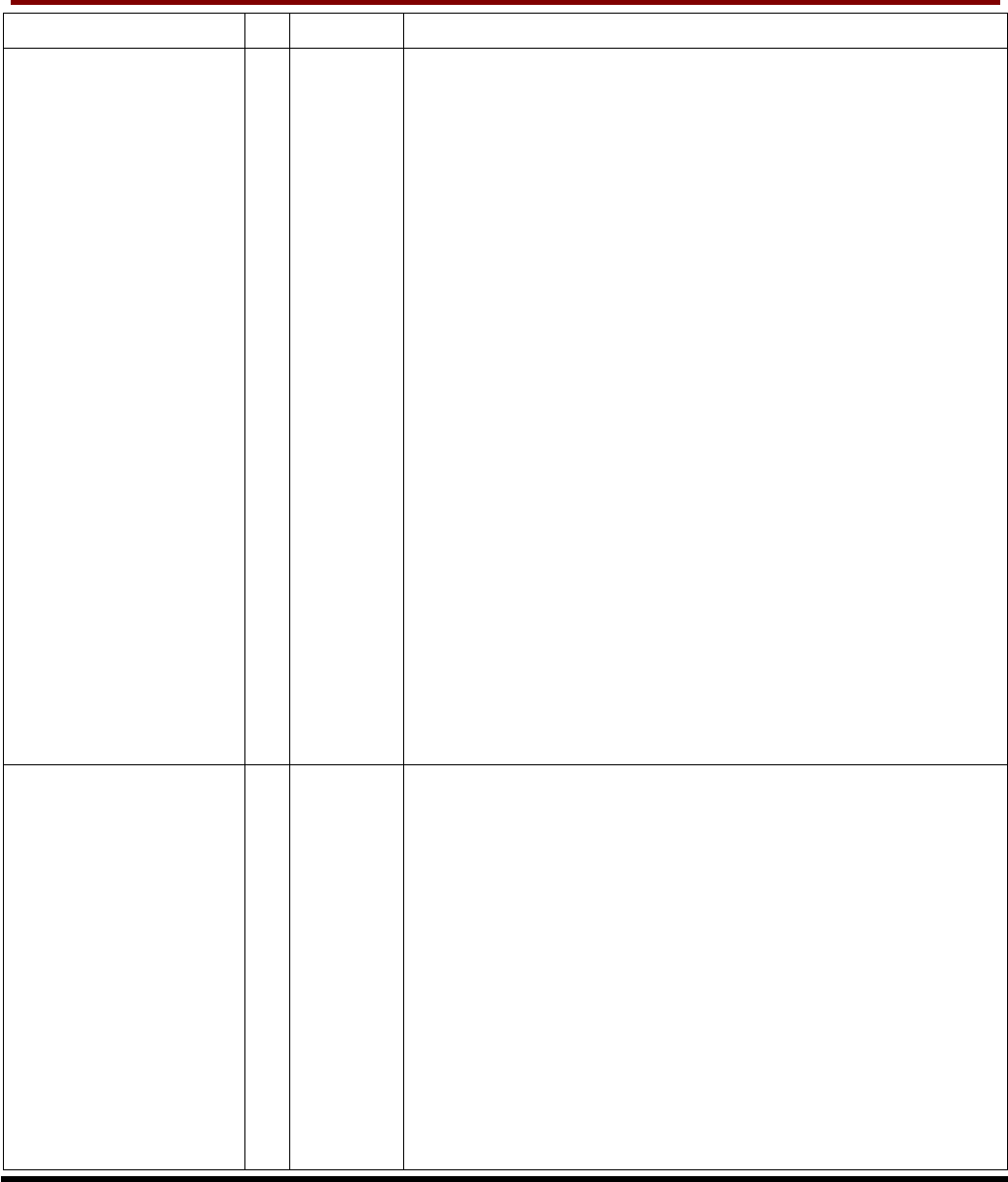

Signal Name

Dir.

Pin

Description

-INPACK

(PC Card Memory Mode except

Ultra DMA Protocol Active)

-INPACK

(PC Card I/O Mode except Ultra

DMA Protocol Active)

Input Acknowledge

-DMARQ

(PC Card Memory Mode -Ultra

DMA Protocol Active)

-DMARQ

(PC Card I/O Mode -Ultra DMA

Protocol Active)

DMARQ

(True IDE Mode)

O

43 This signal is not used in this mode.

The Input Acknowledge signal is asserted by the CompactFlash Storage Card

when the card is selected and responding to an I/O read cycle at the address

that is on the address bus. This signal is used by the host to control the enable

of

any input data buffers between the CompactFlash Storage Card and the CPU.

Hosts that support a single socket per interface logic, such as for Advanced

Timing Modes and Ultra DMA operation may ignore the –INPACK signal from

the device and manage their input buffers based solely on Card Enable signals.

This signal is a DMA Request that is used for DMA data

transfers between host

and device. It shall be asserted by the

device when it is ready to transfer data to

or from the host. For Multiword DMA transfers, the direction of data transfer is

controlled by -HIOE and -IOWR. This signal is used in a

handshake manner with

(-)DMACK, i.e., the device shall wait until the host asserts (-)DMACK before

negating (-)DMARQ, and re-asserting (-)DMARQ if there is more data to

transfer.

In PCMCIA I/O Mode, the

-

DMARQ shall be ignored by the host

while the host is

performing an I/O Read cycle to the device. The host shall not initiate an I/O

Read cycle while

-

DMARQ is asserted by the device.

In True IDE Mode, DMARQ shall not be driven when the device

is not selected in

the Drive-Head register.

While a DMA operation is in progress, -CS0 (-CE1)and -CS1 (-CE2) shall be

held negated and the width of the transfers shall be 16 bits.

If there is no hardware support for True IDE DMA mode in the host, this output

signal is not used and should not be connected at the host. In this case, the

BIOS must report that DMA mode is not supported by the host so that device

drivers will not attempt DMA mode operation.

A host that does not support DMA mode and implements both

PC Card and True

IDE modes of operation need not alter the PC Card mode connections while in

True IDE mode as long as this does not prevent proper operation in any mode.

-HIOE

(PC Card Memory Mode except

Ultra DMA Protocol Active)

-HIOE

(PC Card I/O Mode except Ultra

DMA Protocol Active)

-HIOE

(True IDE Mode – Except Ultra

DMA Protocol Active)

-HDMARDY

(All Modes - Ultra DMA Protocol

DMA Read)

HSTROBE

(All Modes - Ultra DMA Protocol

DMA Write)

I

34 This signal is not used in this mode.

This is an I/O Read strobe generated by the host. This signal

gates I/O data onto

the bus from the CompactFlash Storage

Card when the card is configured to use

the I/O interface.

In True IDE Mode, while Ultra DMA mode is not active, this

signal has the same

function as in PC Card I/O Mode.

In all modes when Ultra DMA mode DMA Read is active, this

signal is asserted

by the host to indicate that the host is ready to receive Ultra DMA data-

in bursts.

The host may negate – HDMARDY to pause an Ultra DMA transfer.

In all modes when Ultra DMA mode DMA Write is active, this signal is the data

out strobe generated by the host. Both the

rising and falling edge of HSTROBE

cause data to be latched by the device. The host may stop generating

HSTROBE edges to pause an Ultra DMA data-out burst.