Data Sheet

MPU-6000/MPU-6050 Product Specification

Document Number: PS-MPU-6000A-00

Revision: 3.4

Release Date: 08/19/2013

19 of 52

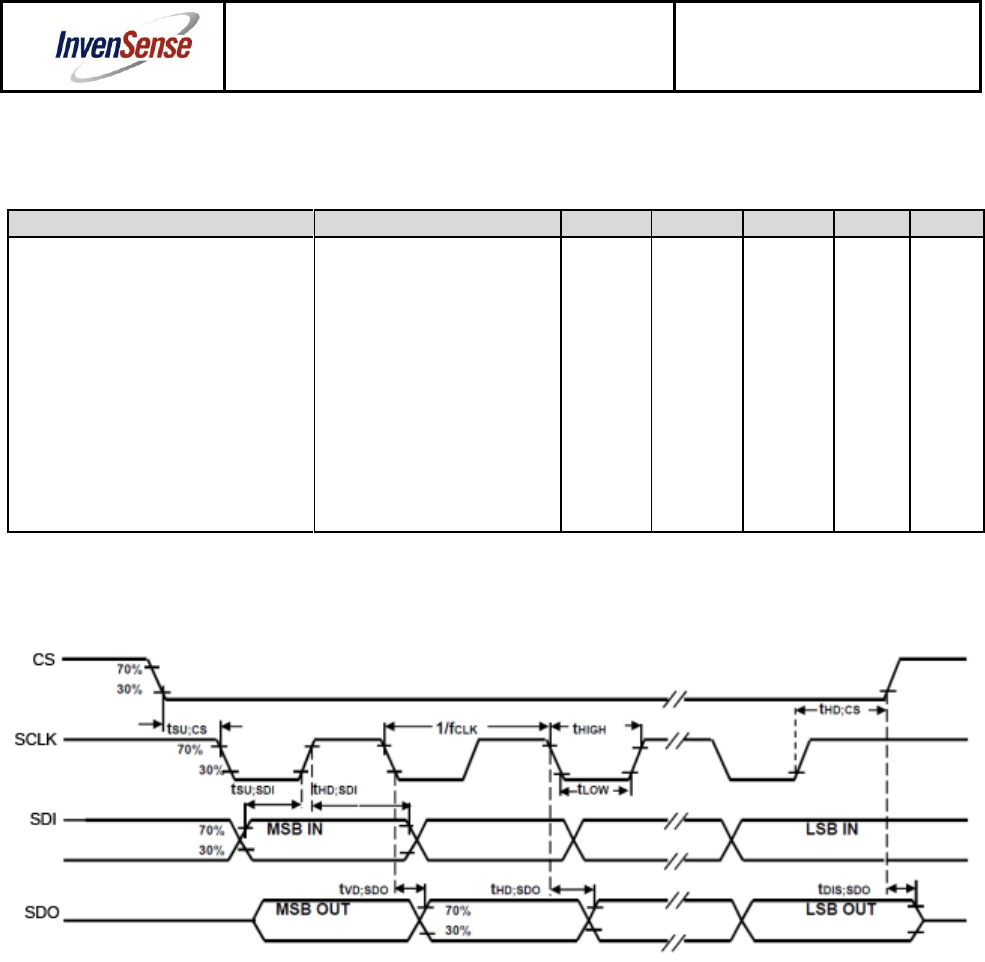

6.8 SPI Timing Characterization (MPU-6000 only)

Typical Operating Circuit of Section 7.2, VDD = 2.375V-3.46V, VLOGIC (MPU-6050 only) = 1.8V±5% or

VDD,T

A

= 25°C, unless otherwise noted.

Parameters

Conditions

Min

Typical

Max

Units

Notes

SPI TIMING

f

SCLK

, SCLK Clock Frequency

1

MHz

t

LOW

, SCLK Low Period

400

ns

t

HIGH

, SCLK High Period

400

ns

t

SU.CS

, CS Setup Time

8

ns

t

HD.CS

, CS Hold Time

500

ns

t

SU.SDI

, SDI Setup Time

11

ns

t

HD.SDI

, SDI Hold Time

7

ns

t

VD.SDO

, SDO Valid Time

C

load

= 20pF

100

ns

t

HD.SDO

, SDO Hold Time

C

load

= 20pF

4

ns

t

DIS.SDO

, SDO Output Disable Time

10

ns

SPI Bus Timing Diagram