Data Sheet

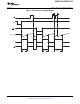

SN54LV123A . . . J OR W PACKAGE

SN74LV123A . . . D, DB, DGV, NS,

OR PW PACKAGE

(TOP VIEW)

SN54LV123A . . . FK PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

1A

1B

1CLR

1Q

2Q

2C

ext

2R

ext

/C

ext

GND

V

CC

1R

ext

/C

ext

1C

ext

1Q

2Q

2CLR

2B

2A

3 2 1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

1C

ext

1Q

NC

2Q

2CLR

1CLR

1Q

NC

2Q

2C

ext

1B

1A

NC

2A

2B

V

1R

2R

GND

NC

CC

NC − No internal connection

ext

/C

ext

ext

/C

ext

SN74LV123A . . . RGY PACKAGE

(TOP VIEW)

1 16

8 9

2

3

4

5

6

7

15

14

13

12

11

10

1R

ext

/C

ext

1C

ext

1Q

2Q

2CLR

2B

1B

1CLR

1Q

2Q

2C

ext

2R

ext

/C

ext

1A

2A

V

GND

CC

SN54LV123A, SN74LV123A

www.ti.com

SCLS393P –APRIL 1998–REVISED OCTOBER 2013

DUAL RETRIGGERABLE MONOSTABLE MULTIVIBRATORS

WITH SCHMITT-TRIGGER INPUTS

Check for Samples: SN54LV123A, SN74LV123A

1

FEATURES

DESCRIPTION

The 'LV123A devices are dual retriggerable

• 2-V to 5.5-V V

CC

Operation

monostable multivibrators designed for 2-V to 5.5-V

• Max t

pd

of 11 ns at 5 V

V

CC

operation.

• Typical V

OLP

(Output Ground Bounce)

These edge-triggered multivibrators feature output

<0.8 V at V

CC

= 3.3 V, T

A

= 25 ° C

pulse-duration control by three methods. In the first

• Typical V

OHV

(Output V

OH

Undershoot)

method, the A input is low, and the B input goes high.

>2.3 V at V

CC

= 3.3 V, T

A

= 25 ° C

In the second method, the B input is high, and the A

input goes low. In the third method, the A input is low,

• Support Mixed-Mode Voltage Operation on All

the B input is high, and the clear (CLR) input goes

Ports

high.

• Schmitt-Trigger Circuitry on A, B, and CLR

The output pulse duration is programmable by

Inputs for Slow Input Transition Rates

selecting external resistance and capacitance values.

• Edge Triggered From Active-High or Active-

The external timing capacitor must be connected

Low Gated Logic Inputs

between C

ext

and R

ext

/C

ext

(positive) and an external

• I

off

Supports Partial-Power-Down Mode

resistor connected between R

ext

/C

ext

and V

CC

. To

Operation

obtain variable pulse durations, connect an external

variable resistance between R

ext

/C

ext

and V

CC

. The

• Retriggerable for Very Long Output Pulses, up

output pulse duration also can be reduced by taking

to 100% Duty Cycle

CLR low.

• Overriding Clear Terminates Output Pulse

• Glitch-Free Power-Up Reset on Outputs

• ESD Protection Exceeds JESD 22

– 2000-V Human-Body Model (A114-A)

– 200-V Machine Model (A115-A)

– 1000-V Charged-Device Model (C101)

• Latch-Up Performance Exceeds 100 mA Per

JESD 78, Class 11

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Copyright © 1998–2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.