User's Manual

VZ22Q LTE Module

V0.1

USI

Confidential Page 9 of 23

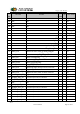

Pin

NO.

Pin name Function

Internal

PU/PD

Type Power domain

29 SDIO_HOST_D3 SDIO DATA 3 I/O 1V8

30 GND GND

31 GND GND

32 GND GND

33 GND GND

34 GND GND

35 PCM_RXD PCM receive data. I 1.8V

36 PCM_CLK PCM clock input, from 128kHz to 8192kHz O 1.8V

37 PCM_FS PCM frame synchroniztion at 8kHz O 1.8V

38 PCM_TXD PCM transmit data. O 1.8V

39

Reserve Reserve test pad for debug

40

Reserve Reserve test pad for debug

41

Reserve Reserve test pad for debug

42 GND GND

43 GND GND

44 ANT1 Antenna 1 I/O

45 GND GND

46 GND GND

47 /RESET Module Rest pin I 1.8V

48 JTAG_TD0 JTAG Test data output O 1.8V

49 JTAG_TRST JTAG Test Reset I 1.8V

50 JTAG_TMS JTAG Test Mode Select I 1.8V

51 JTAG_TDI JTAG Test data input I 1.8V

52 JTAG_TCK JTAG Test Clock I 1.8V

53 GND GND

54 ANT0 Antenna 0 I/O

55 GND GND

56 UART0_SOUT Low speed UART, serial output data, debug only O 1V8

57 AUX_ADC Auxiliary A to D converter I 1V8

58 UART0_SIN Low speed UART, serial input data, debug only I 1V8

59 SPI_SDI Data to SPI device I 1V8

60 SPI_CS_N_1

Active low chip selects to SPI devices.SPI_CS_N[1]

is a primary output, muxed with GPIO[47]

O 1V8

61 SPI_CLK Clock to SPI device. Configurable, up to 61.44MHz O 1V8