User guide

Table Of Contents

- Contents

- 1. About This MegaCore Function Suite

- Release Information

- Device Family Support

- Features

- Design Example

- Performance and Resource Utilization

- 2D FIR Filter

- 2D Median Filter

- Alpha Blending Mixer

- Avalon-ST Video Monitor

- Chroma Resampler

- Clipper

- Clocked Video Input

- Clocked Video Output

- Color Plane Sequencer

- Color Space Converter

- Control Synchronizer

- Deinterlacer

- Deinterlacer II

- Frame Buffer

- Gamma Corrector

- Interlacer

- Scaler

- Scaler II

- Switch

- Test Pattern Generator

- Trace System

- 2. Getting Started with Altera IP Cores

- 3. Interfaces

- Interface Types

- Avalon-ST Video Protocol

- Avalon-MM Slave Interfaces

- Avalon-MM Master Interfaces

- Buffering of Non-Image Data Packets in Memory

- 4. 2D FIR Filter MegaCore Function

- 5. 2D Median Filter MegaCore Function

- 6. Alpha Blending MegaCore Function

- 7. Avalon-ST Video Monitor MegaCore Function

- 8. Chroma Resampler MegaCore Function

- 9. Clipper MegaCore Function

- 10. Clocked Video Input MegaCore Function

- 11. Clocked Video Output MegaCore Function

- 12. Color Plane Sequencer MegaCore Function

- 13. Color Space Converter MegaCore Function

- 14. Control Synchronizer MegaCore Function

- 15. Deinterlacer MegaCore Function

- Core Overview

- Functional Description

- Parameter Settings

- Signals

- Control Register Maps

- 16. Deinterlacer II MegaCore Function

- 17. Frame Reader MegaCore Function

- 18. Frame Buffer MegaCore Function

- 19. Gamma Corrector MegaCore Function

- 20. Interlacer MegaCore Function

- 21. Scaler MegaCore Function

- 22. Scaler II MegaCore Function

- 23. Switch MegaCore Function

- 24. Test Pattern Generator MegaCore Function

- 25. Trace System MegaCore Function

- A. Avalon-ST Video Verification IP Suite

- B. Choosing the Correct Deinterlacer

- Additional Information

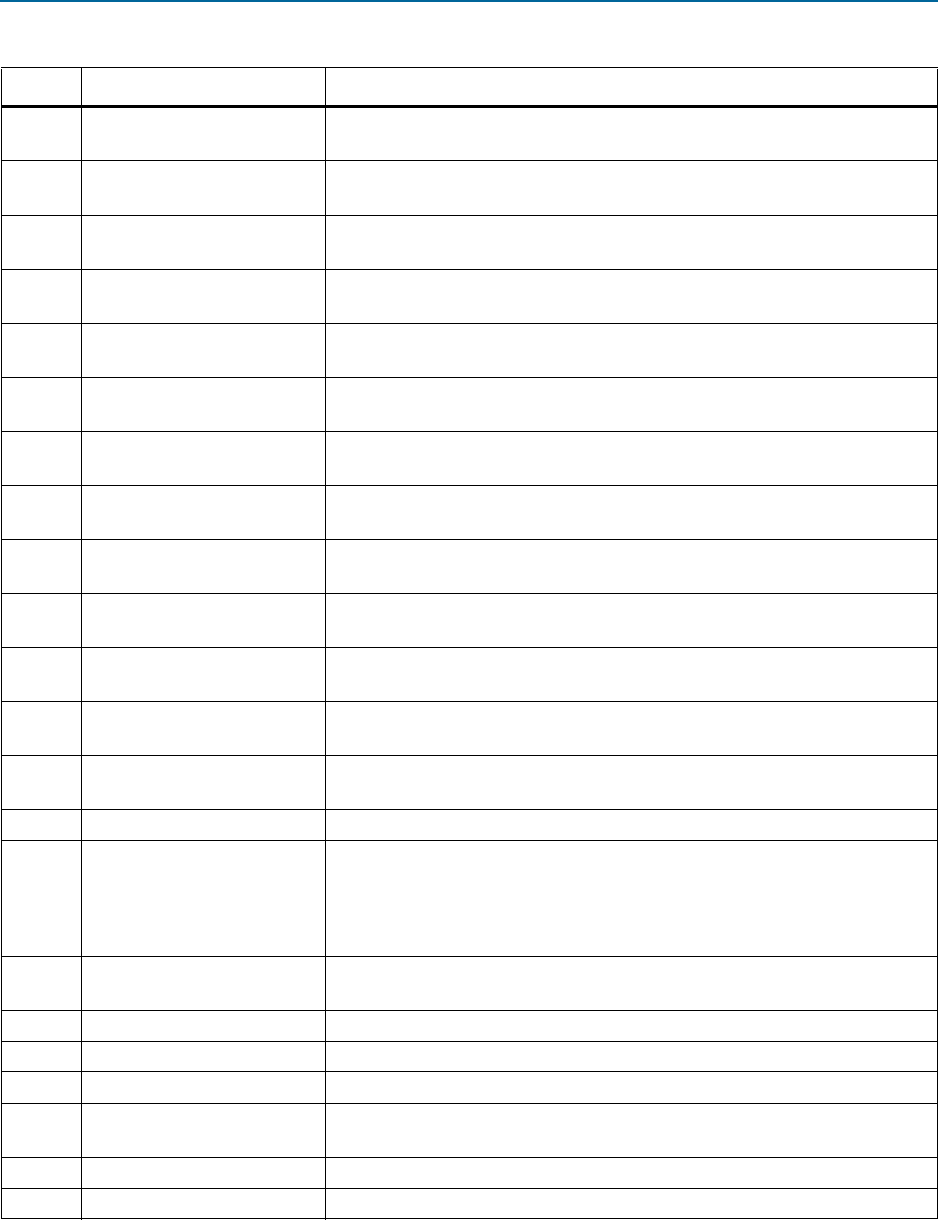

Chapter 11: Clocked Video Output MegaCore Function 11–19

Control Register Maps

January 2013 Altera Corporation Video and Image Processing Suite

User Guide

9

Mode1 Horizontal Front

Porch

Video mode 1 horizontal front porch. Specifies the length of the horizontal front

porch in samples.

10

Mode1 Horizontal Sync

Length

Video mode 1 horizontal synchronization length. Specifies the length of the

horizontal synchronization length in samples.

11

Mode1 Horizontal

Blanking

Video mode 1 horizontal blanking period. Specifies the length of the horizontal

blanking period in samples.

12

Mode1 Vertical Front

Porch

Video mode 1 vertical front porch. Specifies the length of the vertical front porch

in lines.

13

Mode1 Vertical Sync

Length

Video mode 1 vertical synchronization length. Specifies the length of the vertical

synchronization length in lines.

14

Mode1 Vertical Blanking

Video mode 1 vertical blanking period. Specifies the length of the vertical

blanking period in lines.

15

Mode1 F0 Vertical Front

Porch

Video mode 1 field 0 vertical front porch (interlaced video only). Specifies the

length of the vertical front porch in lines.

16

Mode1 F0 Vertical Sync

Length

Video mode 1 field 0 vertical synchronization length (interlaced video only).

Specifies the length of the vertical synchronization length in lines.

17

Mode1 F0 Vertical

Blanking

Video mode 1 field 0 vertical blanking period (interlaced video only). Specifies

the length of the vertical blanking period in lines.

18

Mode1 Active Picture

Line

Video mode 1 active picture line. Specifies the line number given to the first line

of active picture.

19

Mode1 F0 Vertical

Rising

Video mode 1 field 0 vertical blanking rising edge. Specifies the line number

given to the start of field 0's vertical blanking.

20

Mode1 Field Rising

Video mode 1 field rising edge. Specifies the line number given to the end of

Field 0 and the start of Field 1.

21

Mode1 Field Falling

Video mode 1 field falling edge. Specifies the line number given to the end of

Field 0 and the start of Field 1.

22

Mode1 Standard

The value output on the

vid_std

signal.

23

Mode1 SOF Sample

Start of frame sample register. The sample and subsample upon which the SOF

occurs (and the

vid_sof

signal triggers):

■ Bits 0–1 are the subsample value.

■ Bits 2–15 are the sample value.

24

Mode1 SOF Line

SOF line register. The line upon which the SOF occurs measured from the rising

edge of the F0 vertical sync.

25

Mode1 Vcoclk Divider

Number of cycles of

vid_clk

(

vcoclk

) before

vcoclk_div

signal triggers.

26

Mode1 Ancillary Line

The line to start inserting ancillary data packets.

27

Mode1 F0 Ancillary Line

The line in field F0 to start inserting ancillary data packets.

28

Mode1 Valid

Video mode 1 valid. Set to indicate that this mode is valid and can be used for

video output.

29

Mode2 Control

...

30 ...

(1)

...

Note to Table 11–8:

(1) The rows in the table are repeated in ascending order for each video mode. All of the ModeN registers are write only.

Table 11–8. Clocked Video Output Control Register Map (Part 2 of 2)

Address Register Description