user manual

12 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Chapter 1: MicroBlaze Architecture

R

In addition to these fixed features the MicroBlaze processor is parametrized to allow

selective enabling of additional functionality. Older (deprecated) versions of MicroBlaze

support a subset of the optional features described in this manual. Only the latest (active)

version of MicroBlaze (v5.00a) supports all options.

Xilinx recommends that all new designs use the latest active version of the MicroBlaze

processor.

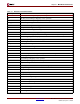

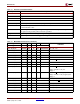

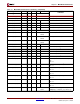

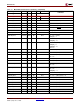

Table 1-1: Configurable Feature Overview by MicroBlaze Version

Feature

MicroBlaze Versions

v2.10a v3.00a v4.00a v5.00a

Version Status deprecated deprecated deprecated active

Processor pipeline depth 3 3 35

On-chip Peripheral Bus (OPB) data side interface option option option option

On-chip Peripheral Bus (OPB) instruction side interface option option option option

Local Memory Bus (LMB) data side interface option option option option

Local Memory Bus (LMB) instruction side interface option option option option

Hardware barrel shifter option option option option

Hardware divider option option option option

Hardware debug logic option option option option

Fast Simplex Link (FSL) interfaces 0-7 0-7 0-7 0-7

Machine status set and clear instructions option option option Yes

Instruction cache over IOPB interface option option option No

Data cache over IOPB interface option option option No

Instruction cache over CacheLink (IXCL) interface - option option option

Data cache over CacheLink (DXCL) interface - option option option

4 or 8-word cache line on XCL - 4 4 option

Hardware exception support - option option option

Pattern compare instructions - - option Yes

Floating point unit (FPU) - - option option

Disable hardware multiplier

1

- - option option

Hardware debug readable ESR and EAR - - Yes Yes

Processor Version Register (PVR) - - - option

1. Used in Virtex-II and subsequent families, for saving MUL18 and DSP48 primitives