Inc. Typewriter User Manual

48 www.xilinx.com MicroBlaze Processor Reference Guide

1-800-255-7778 UG081 (v6.0) June 1, 2006

Chapter 2: MicroBlaze Signal Interface Description

R

On-Chip Peripheral Bus (OPB) Interface Description

The MicroBlaze OPB interfaces are implemented as byte-enable capable masters. Please

refer to the Xilinx OPB design document: “OPB Usage in Xilinx FPGA” for details.

ICache_FSL_out... IXCL_M IO Instruction side CacheLink FSL master

interface

DCache_FSL_in... DXCL_S IO Data side CacheLink FSL slave interface

DCache_FSL_out... DXCL_M IO Data side CacheLink FSL master

interface

Interrupt Core I Interrupt

Reset Core I Core reset, active high. Should be held

for at least 16 cycles

Clk Core I Clock

Debug_Rst Core I Reset signal from OPB JTAG UART,

activehigh.Shouldbeheldforatleast16

cycles

Ext_BRK Core I Break signal from OPB JTAG UART

Ext_NM_BRK Core I Non-maskable break signal from OPB

JTAG UART

Dbg_... Core IO Debug signals from OPB MDM

Valid_Instr Core O Trace: Valid instruction in EX stage

PC_Ex Core O Trace: Address for EX stage instruction

Reg_Write Core O Trace: EX stage instruction writes to the

register file

Reg_Addr Core O Trace: Destination register

MSR_Reg Core O Trace: Current MSR register value

New_Reg_Value Core O Trace: Destination register write data

Pipe_Running Core O Trace: Processor pipeline to advance

Interrup_Taken Core O Trace: Unmasked interrupt hasoccurred

Jump_Taken Core O Trace: Branch instruction evaluated true

Prefetch_Addr Core O Trace: OF stage pointer into prefetch

buffer

MB_Halted Core O Trace: Pipeline is halted

Trace_... Core O Trace signals for real time HW analysis

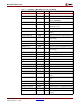

Table 2-1: Summary of MicroBlaze Core I/O (Continued)

Signal Interface I/O Description