Manual

MAX1338

Detailed Description

The MAX1338 simultaneously samples four differential

analog inputs with internal T/H circuits, and sequentially

converts them to a digital code with a 14-bit ADC.

Output data is provided by a 14-bit parallel interface. At

power-up, all channels default to a ±10V input range.

Program different input ranges (±10V, ±5V, ±2.5V, or

±1.25V) using the configuration register. Different input

ranges between ±12V and ±1.0V are realized using an

external reference. All channels offer input protection to

±17V, independent of the selected input range.

The internal clock operates the ADC at 5MHz, or uses

an external conversion clock from 1MHz to 6MHz. EOC

goes low when the result of each conversion is avail-

able, and EOLC goes low when the last conversion

result is available. Standby and shutdown modes,

selectable through logic-control inputs, save power

between conversions. Figure 2 shows a block diagram

of the MAX1338.

14-Bit, 4-Channel, Software-Programmable,

Multiranging, Simultaneous-Sampling ADC

12 ______________________________________________________________________________________

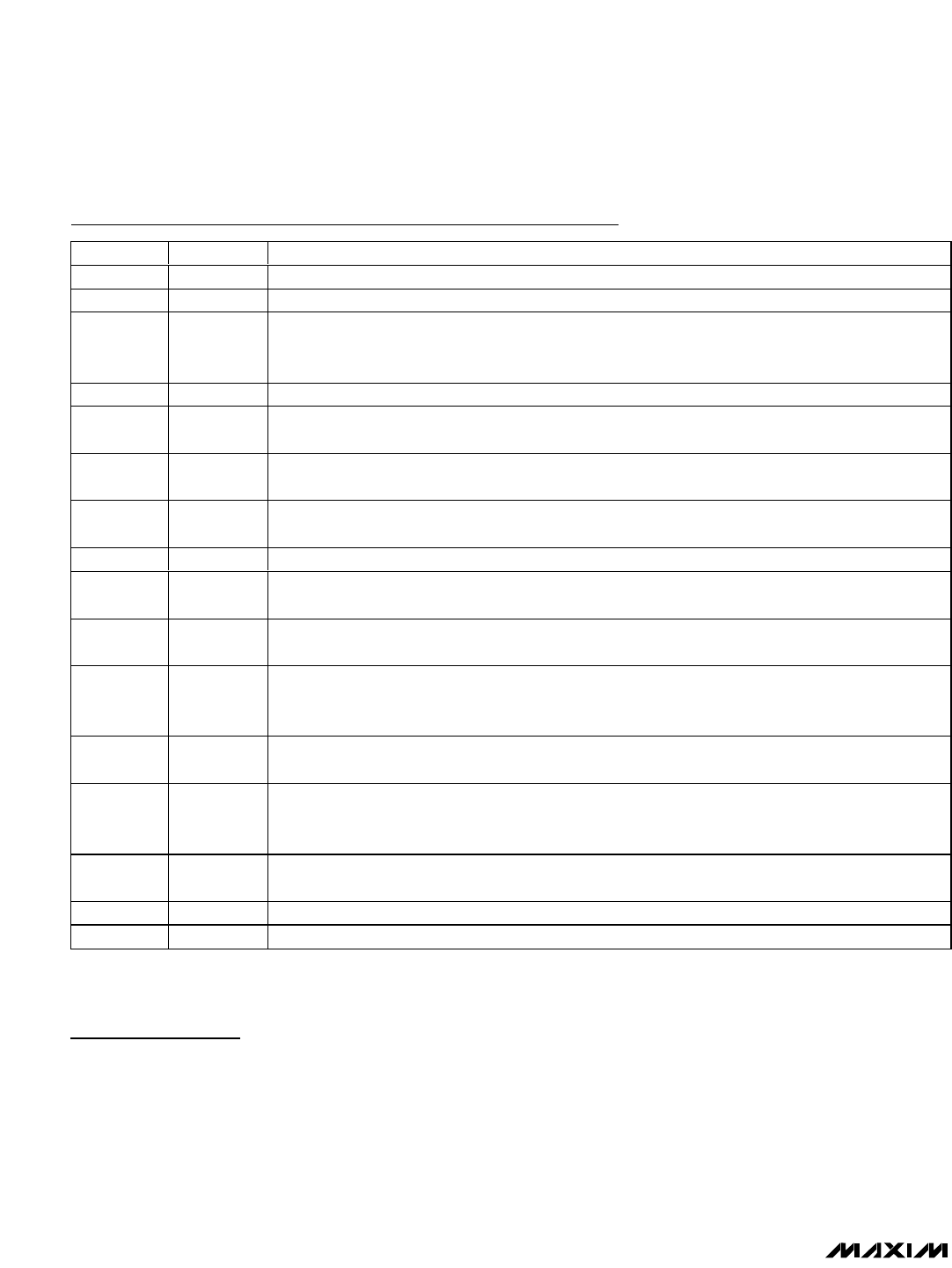

Pin Description (continued)

PIN NAME FUNCTION

41 D12 Data Output Bit 12

42 D13 Data Output Bit 13 (MSB)

43 DRV

DD

Digital I/O Power-Supply Input. DRV

DD

is the power input for the digital I/O buffers and drivers.

Connect a +2.7V to +5.25V power supply to DRV

DD

. Bypass DRV

DD

to DRGND with a 0.1µF

capacitor very close to the device.

44 DRGND Driver Ground. DRGND is the power-supply return for DRV

DD

.

45 EOC

End-of-Conversion Output. EOC goes low to indicate the end of a conversion. EOC returns high after

one clock period.

46 EOLC

End-of-Last-Conversion Output. EOLC goes low to indicate the end of the last conversion. EOLC

returns high when CONVST goes low for the next conversion sequence.

47 RD

Read Input. Forcing RD low initiates a read command of the parallel data bus, D0–D13. D0–D13 are

high impedance while either RD or CS is high.

48 WR Write Input. Forcing WR low initiates a write command for configuring the device through D0–D7.

49 CS

Chip-Select Input. Forcing CS low activates the digital interface. D0–D13 are high impedance while

either CS or RD is high.

50 CONVST

Convert Start Input. CONVST initiates the conversion process. The analog inputs are sampled on the

rising edge of CONVST.

51 CLK

External-Clock Input. CLK accepts a 1MHz to 6MHz external clock signal. For externally clocked

conversions, apply the clock signal to CLK and force INTCLK/EXTCLK low. For internally clocked

conversions, connect CLK to DGND and force INTCLK/EXTCLK high.

52

STANDBY

Standby-Control Input. Forcing STANDBY high partially powers down the device but leaves all the

reference-related circuitry alive. Use STANDBY instead of SHDN when quick wake-up is required.

53 SHDN

Shutdown-Control Input. Force SHDN high to place the device into full shutdown. When in full

shutdown, all circuitry within the device is powered down and all reference capacitors are allowed to

discharge. Allow 1ms for wake-up from full shutdown before starting a conversion.

54 DV

DD

D i g i tal P ow er - S up p l y Inp ut. D V

D D

i s the p ow er i np ut for the d i g i tal ci r cui tr y. C onnect a + 4.75V to + 5.25V

p ow er sup p l y to D V

D D

. Byp ass D V

D D

to D GN D w i th a 0.1µF cap aci tor ver y cl ose to the d evi ce.

55, 56 DGND Digital Ground. Power return for DV

DD

.

—EPExposed Pad. Connect to AGND.